# a

## LF – 2.7 GHz 60 dB TruPwr™ Detector

## **Preliminary Technical Data**

**AD8362**

#### **FEATURES**

True-Power (Root-Mean-Square) Measurement Temperature-Stable Linear-in-dB Response Input Dynamic Range 60 dB  $_{-45}$  to  $_{+15}$  dBm CW Input re: 50  $\Omega$  Flat Response from LF to 2.7 GHz, useful to 3 GHz High Accuracy and Linearity Laser-trimmed Slope of 50 mV/dB Modulation Independent (GSM/W-CDMA/TDMA, etc.) Operation from  $_{-40}$  to  $_{+85}$  °C at  $\rm V_S$  of 4.5 to 5.5 V Powers Down to  $_{-400}$   $\rm \mu W$

#### **APPLICATIONS**

Power Amplifier Linearization/Control Loops Multi-Carrier Transmitter Power Control Rx or Tx Signal Strength Indication (RSSI, TSSI) Instrumentation at LF, HF, VHF, UHF, L- and S-bands

### PRODUCT DESCRIPTION

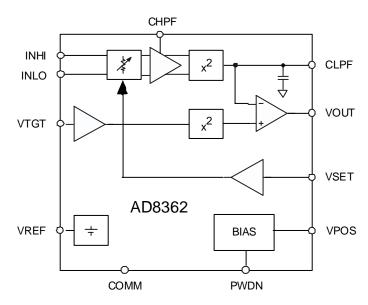

The AD8362 is a true-RMS-responding power detector having a 60 dB measurement range, intended for use in a variety of high-frequency communication and instrumentation systems where an accurate response to signal power is required, regardless of signal waveform. It is fully specified for use at frequencies up to 2.7 GHz. Signal inputs having RMS values from 1.26 mV to 1.26 V (–45 to +15 dBm in a 50  $\Omega$  system) can be accepted. Large crest factors, exceeding the requirements for accurate measurement of CDMA signals, do not degrade accuracy. The AD8362 is easy to use, requiring only a single supply of 5 V plus signal-coupling capacitors (or, in some cases, a balun) and simple decoupling.

The input signal is first applied to a resistive ladder attenuator, having twelve tap-points at about 5 dB intervals. These are smoothly interpolated using a proprietary technique to implement an accurate and continuously-variable attenuator, whose setting is controlled by a voltage applied to pin VSET. The resulting signal is applied to a high-performance broadband amplifier, the output of which is measured by a wideband square-law detector cell. The resulting fluctuating output is then filtered and compared with the output of an identical squarer, whose input is a fixed DC voltage imported via pin VTGT, which will usually be tied to the accurate reference of 1.25 V provided at pin VREF. In some applications, the target voltage (and thus the log intercept) may be altered. The resulting difference in the output of the two squaring cells is then applied to a high-gain error amplifier (an integrator) generating a voltage at pin **VOUT** which can run from rail to rail.

### Rev. PrN 02/14/02

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

When used in a power measurement mode, pin **VOUT** is simply tied to **VSET**, and the output is then proportional to the logarithm of the RMS value of the input. Thus, the reading is scaled directly in decibels, and is conveniently scaled 1 V per decade (50 mV per dB); other slopes are easily arranged. The output can run from ground to a maximum of about 0.1 V below the supply voltage,  $V_S$ . High load currents can be provided.

In controller modes, this low noise signal is used to vary the gain of the host system's RF amplifier, to restore a balance between the set-point demand, determined by the voltage applied to the VSET pin, and a sample of the actual RF power. The set-point voltage may optionally be a baseband replica of the amplitude modulation, in which case the effect is to remove the modulation component prior to detection and low-pass filtering.

For general instrumentation applications, the corner frequency of the averaging filter may be lowered without limit by the addition of an external capacitor at pin **CLPF**. In this way, the AD8362 can be used to determine the RMS value of a low-frequency signal having a complex modulation envelope. The high-pass corner of the broadband amplifier may also need to be lowered by a capacitor added at pin **CHPF**.

The AD8362 may be powered down by a logic voltage applied to the **PWDN** pin, when the current consumption is reduced to under 2  $\mu$ A. The chip powers up to its normal operating current of 18 mA at 25°C within less than 1  $\mu$ s.

The AD8362 is supplied in a 16-pin TSSOP package for operation over the temperature range of -40°C to +85°C.

Multiple patents pending

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 ©Analog Devices, Inc., 2002

## AD8362-SPECIFICATIONS 0 dBV = 1 Vrms)

(Unless otherwise noted,  $V_s = 5 \text{ V}$ ,  $T = 25^{\circ}\text{C}$ ,  $Z_o = 50 \Omega$ , differential input drive, 0 dRV = 1 V/rms)

| Parameters                         | Conditions                                                                                               | Min     | Typ   | Max  | Units  |

|------------------------------------|----------------------------------------------------------------------------------------------------------|---------|-------|------|--------|

| OVERALL FUNCTION                   |                                                                                                          |         |       |      |        |

| Maximum Input Frequency            |                                                                                                          |         | 2.7   |      | GHz    |

| Input Voltage Range                | CW sine wave input                                                                                       | 0.00126 |       | 1.26 | Vrms   |

|                                    |                                                                                                          | -58     |       | +2   | dBV    |

|                                    | Equivalent input power re: $50 \Omega$ (see note 1)                                                      | -45     |       | +15  | dBm    |

| Input Voltage Range                | Single-ended drive, CW sine wave input                                                                   | 1.26    |       | 400  | mVrms  |

|                                    |                                                                                                          | -58     |       | -8   | dBV    |

|                                    | Equivalent input power re: $50 \Omega$ (see note 1)                                                      | -45     |       | +5   | dBm    |

| Measurement Linearity <sup>2</sup> | Over central 50 dB range, 30 MHz $\leq$ f $\leq$ 2.7 GHz                                                 |         | ±0.5  |      | dB     |

|                                    | Over central 60 dB range, 30 MHz $\leq$ f $\leq$ 2.7 GHz                                                 |         | ±1    |      | dB     |

| RF INPUT INTERFACE                 | Pins INHI, INLO, ac coupled                                                                              |         |       |      |        |

| Input Resistance                   | Single-ended drive, wrt <b>DECL</b>                                                                      |         | 100   |      | Ω      |

|                                    | Differential drive                                                                                       |         | 200   |      | Ω      |

| Input Impedance                    | (see performance curves)                                                                                 |         | TBD   |      | Ω      |

| OUTPUT INTERFACE                   | Pin VOUT                                                                                                 |         |       |      |        |

| Voltage Range                      | $R_L \ge 200 \Omega$                                                                                     | 0.5     |       | 4.95 | V      |

| Source/Sink Current                | <b>VOUT</b> held at V <sub>S</sub> /2                                                                    |         | TBD   |      | mA     |

| Small-signal Bandwidth             | $C_L \le 300 \text{ pF}$                                                                                 |         | TBD   |      | MHz    |

| Full-scale Slew Rate               | $C_L \le 300 \text{ pF}$                                                                                 |         | TBD   |      | V/µs   |

| Wideband Noise                     | CLPF = $xxx pF$ , $f_{SPOT} \le 20 MHz$                                                                  |         | TBD   |      | nV/√Hz |

| SET-POINT INPUT                    | Pin VSET                                                                                                 |         |       |      |        |

| Voltage Range                      | Corresponding to 1.126 mV – 1.26 Vrms input signal                                                       | 0.5     |       | 3.5  | V      |

| Input Resistance                   |                                                                                                          |         | 70    |      | kΩ     |

| Logarithmic Scale Factor           | $f = 100 \text{ MHz}, -40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$                              |         | 50    |      | mV/dB  |

| Logarithmic Intercept              | $f = 100 \text{ MHz}, -40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}, \text{ re: } 1 \text{ Vrms}$ |         | -66   |      | dBV    |

|                                    | re: 50 Ω                                                                                                 |         | -53   |      | dBm    |

| Temperature Sensitivity            | $P_{IN} = -10$ dBm, slope and intercept errors combined                                                  |         | TBD   |      | dB/°C  |

| RMS TARGET SET <sup>3</sup>        | Pin VTGT                                                                                                 |         |       |      |        |

| Input Voltage Range                | Measurement range = TBD dB                                                                               | TBD     |       | TBD  | V      |

| Input Bias Current                 | <b>VTGT</b> = 1.25 V                                                                                     |         | -28   |      | uA     |

|                                    | VTGT = 0 V                                                                                               |         | -52   |      | uA     |

| Incremental Input Resistance       |                                                                                                          |         | 52    |      | kΩ     |

| Bandwidth of Target Channel        | To –3 dB point                                                                                           |         | 260   |      | MHz    |

| VOLTAGE REFERENCE                  | Pin VREF                                                                                                 |         |       |      |        |

| Output Voltage                     | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85^{\circ}\text{C}$                                     |         | 1.25  |      | V      |

| Current Limit                      | Into a grounded load                                                                                     |         | TBD   |      | mA     |

| Power Supply Rejection Ratio       |                                                                                                          |         | TBD   |      | V/V    |

| POWER DOWN INTERFACE               | Pin <b>PWDN</b>                                                                                          |         |       |      |        |

| Logic Level to Enable              | Logic LO enables                                                                                         |         |       | TBD  | v      |

| Logic Level to Disable             | Logic HI disables                                                                                        | TBD     |       |      | V      |

| Input Current                      | Logic HI                                                                                                 |         | TBD   |      | uA     |

| _                                  | Logic LO                                                                                                 |         | TBD   |      | uA     |

|                                    |                                                                                                          |         | TID D |      |        |

| Enable Time                        | From <b>PWDN</b> Low to <b>VOUT</b> within 10% of final value                                            |         | TBD   | TBD  | us     |

## PRELIMINARY TECHNICAL DATA

**AD8362**

| Parameters                 | Conditions                                                           | Min | Тур | Max | Units |

|----------------------------|----------------------------------------------------------------------|-----|-----|-----|-------|

| POWER INTERFACE            | Pin VPOS                                                             |     |     |     |       |

| Supply Voltage             |                                                                      | 4.5 | 5   | 5.5 | V     |

| Quiescent Current          |                                                                      |     | 19  | TBD | mA    |

| vs. Temperature            | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85^{\circ}\text{C}$ |     | 19  |     | mA    |

| Supply Voltage Sensitivity |                                                                      | TBD | TBD | TBD | mA/V  |

| Supply Current             | PWDN enabled                                                         |     | TBD |     | μΑ    |

### Notes

- 1. Using an external  $100 \Omega$  resistor connected between **INHI** and **INLO** to produce a net  $50 \Omega$  input resistance.

- 2. Determined by linear regression.

- 3. The voltage required at this pin is 10x the rms value of the steady-state output of the amplifier section.

### ABSOLUTE MAXIMUM RATINGS\*

| Supply Voltage V <sub>POS</sub>                                    |

|--------------------------------------------------------------------|

| Input Power (re: $50 \Omega$ )TBD                                  |

| Equivalent VoltageTBD mVrms                                        |

| Internal Power Dissipation500 mW                                   |

| $\theta_{JA}$ 125 °C/W                                             |

| Maximum Junction Temperature+125 $^{\circ}C$                       |

| Operating Temperature Range $$ 40 $^{\circ}$ C to +85 $^{\circ}$ C |

| Storage Temperature Range $$ 65 $^{\circ}$ C to +150 $^{\circ}$ C  |

| Lead Temperature Range (Soldering 60 sec)+300 °C                   |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### СА ПОЛ

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8362 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy [>250 V HBM] electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### **ORDERING GUIDE**

| Model           | Temp. Range      | Package Description |

|-----------------|------------------|---------------------|

| AD8362ARU       | -40 °C to +85 °C | Tube, 16-Lead TSSOP |

| AD8362ARU-REEL7 |                  | 7" Tape and Reel    |

| AD8362ARU-REEL  |                  | 13" Tape and Reel   |

| AD8362-EVAL     |                  | Evaluation Board    |

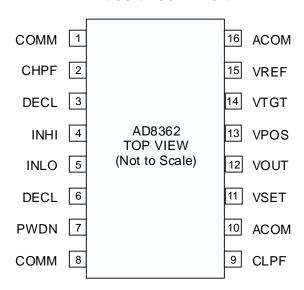

### PIN CONFIGURATION

### **Pin Function Descriptions**

| Pin    | Name | Description                                                                                        | <b>Equivalent Circuit</b> |

|--------|------|----------------------------------------------------------------------------------------------------|---------------------------|

| 1, 8   | COMM | Common connection. Connect via low impedance to system common.                                     |                           |

| 2      | CHPF | Input HPF. Connect to common via a capacitor to determine 3 dB point of input signal high-         |                           |

|        |      | pass filter.                                                                                       |                           |

| 3, 6   | DECL | Decoupling terminals for INHI and INLO. Connect to common via a large capacitance to               |                           |

|        |      | complete input circuit.                                                                            |                           |

| 4      | INHI | "High" signal input terminal. Part of a differential input port with <b>INLO</b> .                 |                           |

| 5      | INLO | "Low" signal input terminal. Part of a differential input port with INHI.                          |                           |

| 7      | PWDN | Disable/Enable control input. Apply logic high voltage to shut AD8362 down.                        |                           |

| 9      | CLPF | Connection for loop filter integration (averaging) capacitor, the other pin of which is usually    |                           |

|        |      | grounded via a resistor to improve loop stability and response time.                               |                           |

| 10, 16 | ACOM | Analog common connection for output amplifier.                                                     |                           |

| 11     | VSET | The voltage applied to this pin sets the decibel value of the required RF input voltage that       |                           |

|        |      | results in zero current out of pin <b>CLPF</b> and thus the loop integrating capacitor.            |                           |

| 12     | VOUT | Output of error amplifier. In measurement mode, normally connected directly to <b>VSET</b> .       |                           |

| 13     | VPOS | Connect to +5 V power supply.                                                                      |                           |

| 14     | VTGT | The logarithmic intercept voltage is proportional to the voltage applied to this pin. The use of a |                           |

|        |      | lower target voltage increases the crest factor capacity.                                          |                           |

| 15     | VREF | General-purpose reference voltage output of 1.25V (usually connected only to <b>VTGT</b> ).        |                           |

## PRELIMINARY TECHNICAL DATA

### **AD8362**

### **Evaluation Board**

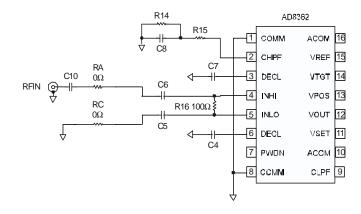

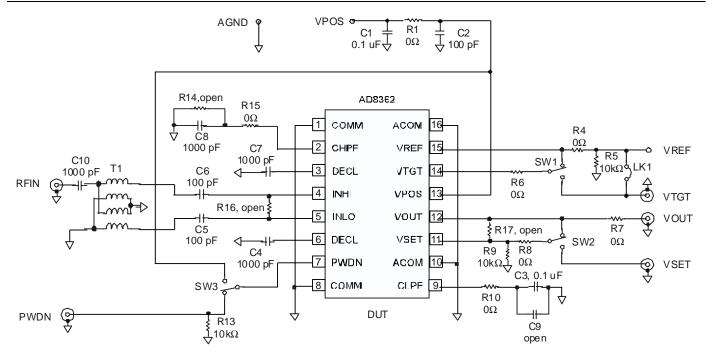

Figure XX shows the schematic of the AD8362 evaluation board. It supports operation of the AD8362 in Measurement Modes or Controller Modes, and allows for the use of the internally-generated reference voltage to be used as the target voltage.

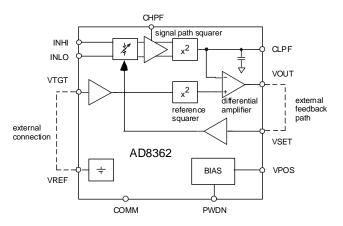

Figure X4 Simplified Block Diagram in Measurement Mode

Figure X4 shows the AD8362 as it could be configured for measurement mode operation. The AD8362 compares an amplified, squared, averaged version of the input signal to a target voltage which has been applied to an identical squaring cell. These voltages are applied to a differential amplifier, the output of which is fed back in Measurement Mode to the gain control of the input variable attenuator. This forces the output of the signal-path squaring cell to be equal to the output of the reference squaring cell. In this mode, the output voltage of the differential amplifier is a linear-in-dB representation of the input signal rms voltage.

### **Input Circuit**

The input to the AD8362 is differential in order to optimize the input measurement range, among other things. A balun can transform a single-ended RF signal to differential form. The ETC1.6-4-2-3, 500 MHz - 2.5 GHz, 4:1 balun is installed on the evaluation board. Note that the RF input impedance at the RFIN connector may not be 50  $\Omega$  unless a balun having the correct ratio is used. If the AD8362 is to be evaluated at frequencies higher than 2.5 GHz or lower than 500 MHz, better performance will be obtained if this balun is replaced with one that is designed for those frequencies.

It is important to note that the balun transformer steps up the signal voltage by the square root of its turns ratio.

Thus, the signal voltage at the output of T1 is 6 dB larger than at its input. This is effectively the input signal magnitude which the AD8362 measures.

The AD8362 eval board has been designed to accommodate other single-ended interfaces. If either of the configurations described below are used, balun T1 may be eliminated, at the expense of a 6 dB reduction in measurement range at the high end and reduced sensitivity to very small signals.

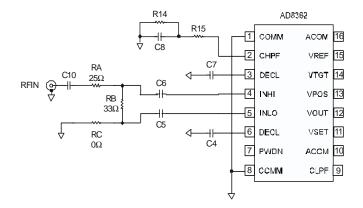

Balun T1 may be removed and replaced with two resistors which will match a 50  $\Omega$  source to the input impedance of the AD8362. In this case, RA should be 25  $\Omega$  and RB should be 33  $\Omega$ , as shown in Figure X2. Note that the unused input to the AD8362 must be ac-coupled to ground, via capacitor C5 and the 0  $\Omega$  resistor RC. In this configuration, R16 is open.

Figure X2 Single-ended Drive Without a Balun – Option A

Alternatively, T1 may be removed, a 0  $\Omega$  resistor installed at positions RA and RC and a 100  $\Omega$  resistor installed at R16, as shown in Figure X3.

Figure X3 Single ended Drive without a Balun – Option B

### **Target Voltage**

The target voltage can be used to adjust the intercept of the AD8362 transfer function. Nominally, the voltage applied to **VTGT** is the stable, 1.25 V reference voltage produced by a band gap cell on the AD8362, which is available at **VREF**. This is the case when SW1 is in the position shown in Figure XX.

If the voltage at **VTGT** is lowered the intercept is increased, which allows the AD8362 to accurately measure signals with larger crest factors, at the expense of reduced sensitivity to very small input signals. This can be accomplished by installing the appropriate resistor values for R4 and R5, and switching SW1 to connect **VTGT** to LK1. The input incremental resistance at pin VTGT is nominally  $52 \text{ k}\Omega$ , so the value of R5 should be calculated with this in mind.

An external voltage may be applied to connector VTGT. In this case, LK1 should be removed. The external voltage may be a dc voltage higher than that available from **VREF**, which would improve the sensitivity of the AD8362 to small input signals, at the expense of reduced ability to measure large input signals.

### **Measurement Mode**

The AD8362 can be configured in Measurement Mode by externally completing a feedback path from **VOUT** to **VSET**. The slope of the transfer function can be altered by controlling the portion of the voltage present at **VOUT** that is applied to **VSET**. If the entire signal from **VOUT** is applied to **VSET**, as is the case when SW2 is in the position shown in Figure XX, the slope of the transfer function is nominally 50 mV per dB.

The transfer function slope can be increased by adding an external resistor between **VOUT** to **VSET**, which is R17 on the eval board. If this configuration is used, then SW2 should be switched from the position shown in Figure XX or the 0  $\Omega$  resistor at R8 should be removed. R9 should be removed from the evaluation board.

$$R_{17} = R_{IN} * \left(\frac{NS}{OS} - 1\right)$$

R17 forms a voltage divider with the input resistance of VSET, as shown is Figure X4. The formula for R17, in terms of the desired slope (NS), original slope (OS) and input resistance of VSET (RIN) is

Since the value of RIN is not tightly controlled or guaranteed, it may be helpful to add an external shunt resistor, in position R9, whose resistance is smaller than the nominal value of RIN, thereby decreasing the sensitivity of the new slope to process variations that might cause the value of RIN to change. In this case, the equation that defines the value of R17 is

$$R_{17} = \left(\frac{R_{IN} * R_9}{R_{IN} + R_9}\right) * \left(\frac{NS}{OS} - 1\right)$$

If this configuration is used, it is important to provide sufficient load impedance to pin **VOUT** to ensure that it will not be called upon to source more than its specified source /sink current.

### **Controller Mode**

The AD8362 can be configured to operate as a controller, the operation of which is analogous to a comparator. In this configuration, there is no feedback path between pins **VOUT** and **VSET**, so SW2 should be switch from the position shown in Figure XX and R17 should be open.

A set-point voltage is applied to pin **VSET**. If the input signal magnitude is lower than that which corresponds to the set-point voltage, the voltage at pin **VOUT** is a logic low. If the input signal magnitude is increased to a value larger than that which corresponds to the set-point voltage, the voltage at pin **VOUT** will go to logic high.

The set-point voltage that will cause the AD8362 to toggle at a given input signal level is simply the voltage would be produced at **VOUT** if the AD8362 were configured in Measurement Mode.

### **Power Down**

Switch SW3 allows the **PWDN** pin to be connected either to the supply line voltage,  $V_{POS}$ , in order to disable the AD8362, or to a pull-down resistor to which an externally-generated logic level may be applied. The AD8362 is enabled by a low logic level applied to the **PWDN** pin, which may also be directly grounded.

Figure XX. Evaluation Board Schematic

**Table II Evaluation Board Configuration Options**

| Component                       | Function                                                           | Part Number  | Default Value                    |

|---------------------------------|--------------------------------------------------------------------|--------------|----------------------------------|

| T1                              |                                                                    | ETC1.6-4-2-3 |                                  |

| C1                              | Supply filtering/decoupling capacitor                              |              | 0.1 μF                           |

| C2                              | Supply filtering/decoupling capacitor                              |              | 100 pF                           |

| C3                              | Output low pass filter capacitor                                   |              | 0.1 μF                           |

| C9                              | Output low pass filter capacitor (normally omitted, not installed) |              |                                  |

| C4, C7, C10                     | Input bias-point decoupling capacitors                             |              | 1000 pF                          |

| C5, C6                          | Input signal coupling capacitors                                   |              | 100 pF                           |

| C8                              | Input high pass filter capacitor                                   |              | 1000 pF                          |

| DUT                             | AD8362                                                             | AD8362ARU    |                                  |

| R1, R4, R6, R7,<br>R8, R10, R15 |                                                                    |              | 0 Ω                              |

| R5, R9, R13                     | Optional pull-down resistors                                       |              | 10k Ω                            |

| R16                             | (not installed, see text)                                          |              | 100 Ω                            |

| R17                             | Slope adjustment (not installed, see text)                         |              | (See text)                       |

| RA                              | (Not installed, see text)                                          |              | $25 \Omega \text{ or } 0 \Omega$ |

| RB                              | (Not installed, see text)                                          |              | 33 Ω                             |

| RC                              | (Not installed, see text)                                          |              | 0 Ω                              |

| SW1                             | Internal/external target voltage selector                          |              |                                  |

| SW2                             | Measurement mode/controller mode selector                          |              |                                  |

| SW3                             | Powerdown/enable or external power down selector                   |              |                                  |

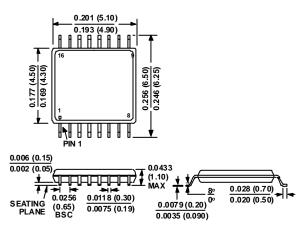

### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

### 16-Lead TSSOP (RU-16)

SUNSTAR商斯达实业集团是集研发、生产、工程、销售、代理经销 、技术咨询、信息服务等为一体的高 科技企业,是专业高科技电子产品生产厂家,是具有10多年历史的专业电子元器件供应商,是中国最早和 最大的仓储式连锁规模经营大型综合电子零部件代理分销商之一,是一家专业代理和分銷世界各大品牌IC 芯片和電子元器件的连锁经营綜合性国际公司。在香港、北京、深圳、上海、西安、成都等全国主要电子 市场设有直属分公司和产品展示展销窗口门市部专卖店及代理分销商,已在全国范围内建成强大统一的供 货和代理分销网络。 我们专业代理经销、开发生产电子元器件、集成电路、传感器、微波光电元器件、工 控机/DOC/DOM电子盘、专用电路、单片机开发、MCU/DSP/ARM/FPGA软件硬件、二极管、三极管、模 块等,是您可靠的一站式现货配套供应商、方案提供商、部件功能模块开发配套商。专业以现代信息产业 (计算机、通讯及传感器)三大支柱之一的传感器为主营业务,专业经营各类传感器的代理、销售生产、 网络信息、科技图书资料及配套产品设计、工程开发。我们的专业网站——中国传感器科技信息网(全球 传感器数据库)www.SENSOR-IC.COM 服务于全球高科技生产商及贸易商,为企业科技产品开发提供技 术交流平台。欢迎各厂商互通有无、交换信息、交换链接、发布寻求代理信息。欢迎国外高科技传感器、 变送器、执行器、自动控制产品厂商介绍产品到 中国,共同开拓市场。本网站是关于各种传感器-变送器-仪器仪表及工业自动化大型专业网站,深入到工业控制、系统工程计 测计量、自动化、安防报警、消费电 子等众多领域, 把最新的传感器-变送器-仪器仪表买卖信息, 最新技术供求, 最新采购商, 行业动态, 发展方 向,最新的技术应用和市场资讯及时的传递给广大科技开发、科学研究、产品设计人员。本网站已成功为 石油、化工、电力、医药、生物、航空、航天、国防、能源、冶金、电子、工业、农业、交通、汽车、矿 山、煤炭、纺织、信息、通信、IT、安防、环保、印刷、科研、气象、仪器仪表等领域从事科学研究、产 品设计、开发、生产制造的科技人员、管理人员 、和采购人员提供满意服务。 我公司专业开发生产、代 理、经销、销售各种传感器、变送器、敏感元器件、开关、执行器、仪器仪表、自动化控制系统: 专门从 事设计、生产、销售各种传感器、变送器、各种测控仪表、热工仪表、现场控制器、计算机控制系统、数 据采集系统、各类环境监控系统、专用控制系统应用软件以及嵌入式系统开发及应用等工作。如热敏电阻、 压敏电阻、温度传感器、温度变送器、湿度传感器、 湿度变送器、气体传感器、 气体变送器、压力传感 器、 压力变送、称重传感器、物(液)位传感器、物(液)位变送器、流量传感器、 流量变送器、电流 (压) 传感器、溶氧传感器、霍尔传感器 、图像传感器、超声波传感器、位移传感器、速度传感器、加速 度传感器、扭距传感器、红外传感器、紫外传感器、 火焰传感器、激光传感器、振动传感器、轴角传感器、 光电传感器、接近传感器、干簧管传感器、继电器传感器、微型电泵、磁敏(阻)传感器 、压力开关、接 近开关、光电开关、色标传感器、光纤传感器、齿轮测速传感器、 时间继电器、计数器、计米器、温控仪、 固态继电器、调压模块、电磁铁、电压表、电流表等特殊传感器。 同时承接传感器应用电路、产品设计 和自动化工程项目。

### 更多产品请看本公司产品专用销售网站:

商斯达中国传感器科技信息网: http://www.sensor-ic.com/

商斯达工控安防网: http://www.pc-ps.net/

商斯达电子 元器件网: http://www.sunstare.com/

商斯达微波光电产品网:HTTP://www.rfoe.net/

商斯达消费电子产品网://www.icasic.com/

商斯达军工产品网:http://www.junpinic.com/

商斯达实业科技产品网://www.sunstars.cn/传感器销售热线:

地址:深圳市福田区福华路福庆街鸿图大厦 1602 室

电话: 0755-83607652 83376489 83376549 83370250 83370251 82500323

传真: 0755-83376182 (0) 13902971329 MSN: SUNS8888@hotmail.com

邮编: 518033 E-mail:szss20@163.com QQ: 195847376

深圳赛格展销部: 深圳华强北路赛格电子市场 2583 号 电话: 0755-83665529 25059422

技术支持: 0755-83394033 13501568376

欢迎索取免费详细资料、设计指南和光盘 ; 产品凡多,未能尽录,欢迎来电查询。

北京分公司:北京海淀区知春路 132 号中发电子大厦 3097 号

TEL: 010-81159046 82615020 13501189838 FAX: 010-62543996

上海分公司: 上海市北京东路 668 号上海賽格电子市场 D125 号

TEL: 021-28311762 56703037 13701955389 FAX: 021-56703037

西安分公司: 西安高新开发区 20 所(中国电子科技集团导航技术研究所)

西安劳动南路 88 号电子商城二楼 D23 号

TEL: 029-81022619 13072977981 FAX:029-88789382