**E2F0007-18-11** SUNSTAR电子元器件 http://www.sunstare.com/ TEL: 0755-83376282 FAX:0755-83376182 E-MAIL:szss20@163.com This version: Jan. 1998

# **MSM9405**

IrDA Communication Controller

# **GENERAL DESCRIPTION**

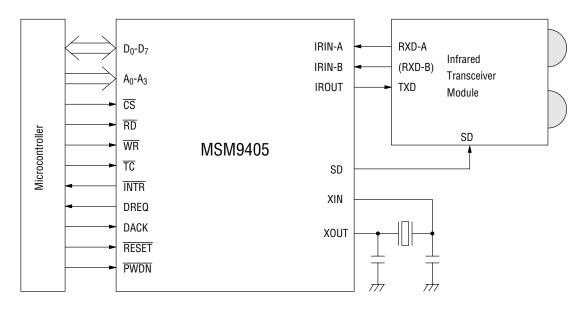

The MSM9405 is a communication controller conforming to IrDA, the international standard for infrared data communication. The device covers the IrDA physical specifications Ver.1.0 and 1.1.

Since the device performs some of the functions concerning communication protocol control, the load on the software (firmware) for protocol control can be reduced. By combining the device with another microcontroller and an infrared transceiver module, a device provided with IrDA-compliant communication function can be configured.

# FEATURES

| • Data transfer rates |                                                |

|-----------------------|------------------------------------------------|

| IrDA 1.0              | : 2400, 9600 bps; 19.2, 38.4, 57.6, 115.2 kbps |

| IrDA 1.1              | : 0.576, 1.152, 4 Mbps                         |

• Detection/removal for beginning of frame and end of frame (IrDA 1.0, 1.1)

Insertion for beginning of frame and end of frame (IrDA 1.0, 1.1)

- Generation/check for CRC (IrDA 1.0, 1.1)

- Host interface

- 8-bit data bus  $: D_0 - D_7$ DMA transfer : DREQ, DACK,  $\overline{TC}$ Interrupt : INTR Address  $: A_0 - A_3$  $: \overline{CS}, \overline{RD}, \overline{WR}$ Control signal

- Infrared module control signal : SD

- Built-in 32-byte transmit-receive FIFOs

- Power down mode

- Built-in oscillator circuit

- Crystal oscillation frequency : 18.432 MHz (other than 4 Mbps data rate) : 48 MHz (when 4 Mbps data rate used)

- Operating voltage (V<sub>DD</sub>) : 2.7 to 3.6 V

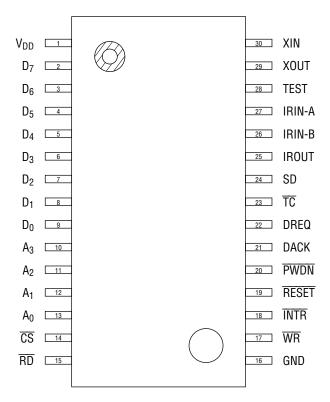

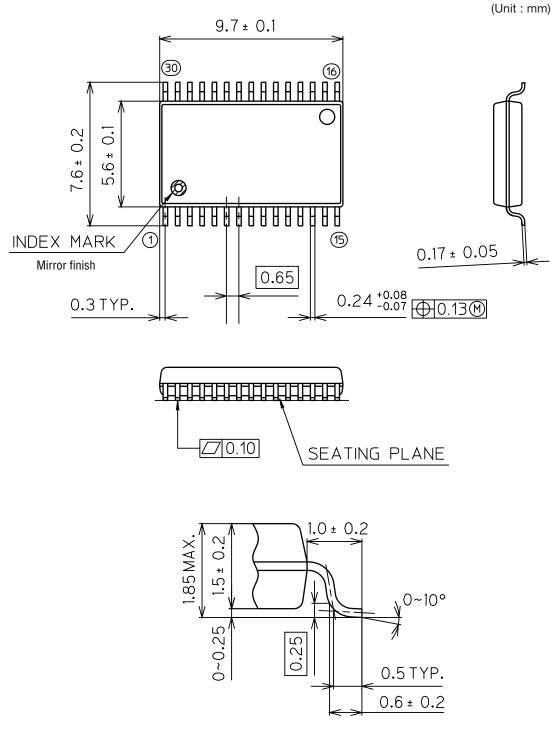

- Package: 30-pin plastic SSOP (SSOP30-P-56-0.65-K) (Product name : MSM9405MB)

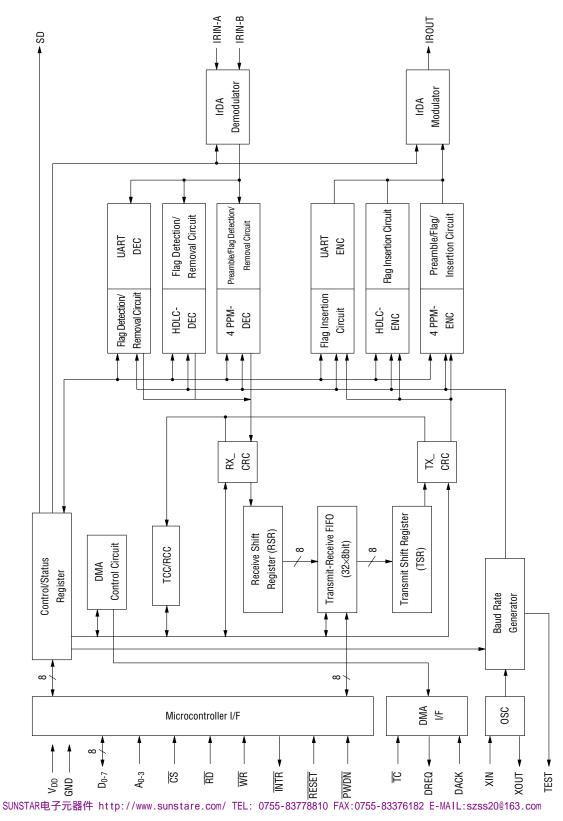

## **BLOCK DIAGRAM**

**MSM9405**

# **PIN CONFIGURATION (TOP VIEW)**

# **PIN DESCRIPTIONS**

| Function         | Pin   | Symbol                         | Туре | Description                                                  |

|------------------|-------|--------------------------------|------|--------------------------------------------------------------|

| Transceiver      | 27    | IRIN-A                         | I    | Receive signal input A. (2.4 kbps to 4 Mbps) <sup>*1</sup>   |

| Module Interface | 26    | IRIN-B                         | I    | Receive signal input B. (0.576 to 4 Mbps)                    |

|                  |       |                                |      | When connecting this device to a transceiver module,         |

|                  |       |                                |      | tie this pin high or low if the number of the receive signal |

|                  |       |                                |      | output pins that the module has is only one. <sup>*1</sup>   |

|                  | 25    | IROUT                          | 0    | Transmit signal output. Active high.                         |

|                  | 24    | SD                             | 0    | Transceiver module control signal output.                    |

|                  |       |                                |      | Becomes active when PWDN is set low. <sup>*1</sup>           |

|                  |       |                                |      | This pin must be left open if connecting this device to a    |

|                  |       |                                |      | transceiver module having no shutdown pins.                  |

| Microcontroller  | 9-2   | D <sub>0</sub> -D <sub>7</sub> | I/0  | Data input-output.                                           |

| Interface        | 13-10 | A <sub>0</sub> -A <sub>3</sub> | I    | Register address inputs.                                     |

|                  | 14    | CS                             | I    | Chip select input. Active low.                               |

|                  |       |                                |      | When low, read and write signals are enabled.                |

|                  | 15    | RD                             | I    | Read signal input. Active low.                               |

|                  | 17    | WR                             | I    | Write signal input. Active low.                              |

|                  | 18    | INTR                           | 0    | Interrupt request signal output. Active low.                 |

| DMA Controller   | 22    | DREQ                           | 0    | DMA Request signal output. <sup>*1</sup>                     |

| Interface        | 21    | DACK                           | I    | DMA acknowledge signal input. <sup>*1</sup>                  |

|                  | 23    | TC                             | I    | DMA transfer end signal input. Active low.                   |

| Others           | 20    | PWDN                           | I    | Power down control. Active low.                              |

|                  |       |                                |      | When set low, oscillation stops and the device enters power  |

|                  |       |                                |      | down (low supply current) mode.                              |

|                  | 19    | RESET                          | I    | System reset input. Active low.                              |

|                  |       |                                |      | When set low, the internal registers are initialized.        |

|                  | 28    | TEST                           | 0    | Test. Must be left open.                                     |

|                  | 30    | XIN                            | I    | Crystal connect.                                             |

|                  | 29    | XOUT                           | 0    | Crystal connect.                                             |

|                  | 1     | V <sub>DD</sub>                | _    | Power supply.                                                |

|                  | 16    | GND                            | _    | Ground.                                                      |

\*1 Either active high or active low can be selected depending on the register setting.

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter           | Symbol           | Condition | Rating       | Unit |

|---------------------|------------------|-----------|--------------|------|

| Supply Voltage      | V <sub>DD</sub>  | —         | -0.5 to +4.0 | V    |

| Input Voltage       | VI               | —         | -0.5 to +6.0 | V    |

| Power Dissipation   | PD               |           | 230          | mW   |

| Storage Temperature | T <sub>STG</sub> |           | -55 to +150  | °C   |

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter             | Symbol          | Condition | Range                                    | Unit |

|-----------------------|-----------------|-----------|------------------------------------------|------|

| Supply Voltage        | V <sub>DD</sub> | _         | 2.7 to 3.6                               | V    |

| Operating Temperature | T <sub>op</sub> | —         | -20 to +70                               | °C   |

| Crystal Oscillation   | faaa            |           | 19 422 MHz , 200 ppm or 49 MHz , 100 ppm |      |

| Frequency             | tosc            |           | 18.432 MHz ±200 ppm or 48 MHz ±100 ppm   |      |

# **ELECTRICAL CHARACTERISTICS**

## **DC** Characteristics

#### $(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{ Ta} = -20 \text{ to } +70^{\circ}\text{C})$

|                       |                  |                        | _        |      | (•00              |      |                                                                       |  |

|-----------------------|------------------|------------------------|----------|------|-------------------|------|-----------------------------------------------------------------------|--|

| Parameter             | Symbol           | Condition              | Min.     | Тур. | Max.              | Unit | Applicable Pin                                                        |  |

| "H" Input Voltage     | VIH              | —                      | 2.2      | —    | 5.5               | v    | IRIN-A, IRIN-B, PWDN                                                  |  |

| "L" Input Voltage     | V <sub>IL</sub>  | —                      | 0        | —    | 0.8*1             | V    | $A_0$ - $A_3$ , $\overline{CS}$ , $\overline{RD}$ , $\overline{WR}$ , |  |

| Input Leakage Current | ILI              | $V_I = V_{DD}/0 V$     |          | —    | ±1                | μA   | TC, RESET, DACK                                                       |  |

| "H" Input Voltage     | VIH              |                        | 2.2      | —    | 5.5               | V    |                                                                       |  |

| "L" Input Voltage     | VIL              |                        | 0        | —    | 0.8 <sup>*1</sup> | V    |                                                                       |  |

| Input Leakage Current | ILI              | $V_I = V_{DD}/0 V$     |          | —    | ±10               | μA   | D <sub>0</sub> -D <sub>7</sub>                                        |  |

| "H" Output Voltage    | V <sub>OH</sub>  | $I_0 = -4 \text{ mA}$  | 2.4      | —    | —                 | v    |                                                                       |  |

| "L" Output Voltage    | V <sub>OL</sub>  | $I_0 = 4 \text{ mA}$   | _        | —    | 0.4               | V    |                                                                       |  |

| "H" Output Voltage    | V <sub>OH</sub>  | I <sub>0</sub> = -4 mA | 2.4      | —    | —                 | v    |                                                                       |  |

| "L" Output Voltage    | V <sub>OL</sub>  | $I_0 = 4 \text{ mA}$   | 4 mA — — |      | 0.4               | V    | IROUT, INTR, DREQ                                                     |  |

| Supply Current        | I <sub>DD</sub>  |                        |          | —    | 20                | mA   | V <sub>DD</sub>                                                       |  |

| Supply Current        | 1                | M/han DM/DN "I "       |          |      |                   |      | M                                                                     |  |

| (during Power Down)   | I <sub>DPN</sub> | When PWDN = "L"        |          |      |                   | μA   | V <sub>DD</sub>                                                       |  |

\*1 1.0 V when  $V_{DD}$  = 3.0 to 3.6 V

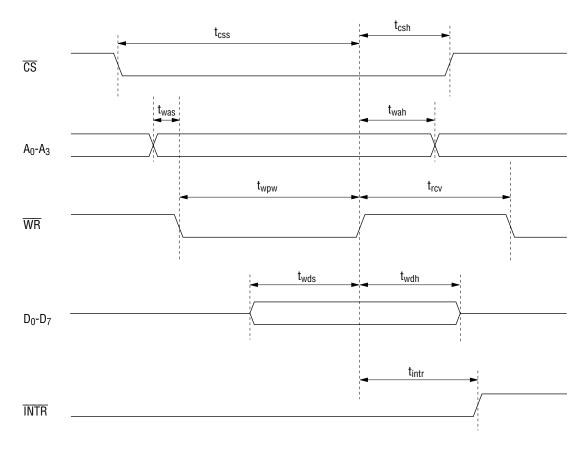

## **AC Characteristics**

| Parameter                     | Symbol            | Condition   | Min.   | Тур. | Max.   | Unit | Note |

|-------------------------------|-------------------|-------------|--------|------|--------|------|------|

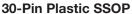

| Read Pulse Width              | t <sub>rpw</sub>  |             | 120/70 | _    |        | ns   | *1   |

| Read Data Delay Time          | t <sub>rdd</sub>  | _           | _      |      | 60     | ns   | *2   |

| Read Data Hold Time           | t <sub>rdh</sub>  | _           | 0      |      | 20     | ns   | *3   |

| Read/Write Recovery Time      | t <sub>rcv</sub>  | _           | 60     |      | _      | ns   |      |

| CS Setup Time                 | t <sub>css</sub>  | _           | 60     |      | _      | ns   |      |

| CS Hold Time                  | t <sub>csh</sub>  | _           | 0      |      | _      | ns   |      |

| Write Address Hold Time       | t <sub>wah</sub>  |             | 0      |      | _      | ns   |      |

| Write Pulse Width             | t <sub>wpw</sub>  | _           | 120/70 | _    | _      | ns   | *1   |

| Write Data Setup Time         | t <sub>wds</sub>  | _           | 60     |      | _      | ns   |      |

| Write Data Hold Time          | t <sub>wdh</sub>  | _           | -10    |      | _      | ns   |      |

| Write Address Setup Time      | t <sub>was</sub>  | _           | -10    |      | _      | ns   |      |

| Interrupt Clear Time          | t <sub>intr</sub> | _           |        |      | 120/70 | ns   | *1   |

| DACK Pulse Width              | t <sub>dak</sub>  | _           | 60     |      | _      | ns   |      |

| DACK Setup Time               | t <sub>acs</sub>  | _           | 10     |      |        | ns   |      |

| DREQ Clear Time               | t <sub>drqr</sub> | _           |        |      | 120/70 | ns   | *1   |

| DACK Hold Time (during Read)  | t <sub>achr</sub> | _           | -5     |      |        | ns   |      |

| DACK Hold Time (during Write) | t <sub>achw</sub> | _           | 10     |      |        | ns   |      |

| TC Pulse Width                | t <sub>tcw</sub>  | _           | 50     |      | _      | ns   |      |

| TC Setup Time                 | t <sub>tcs</sub>  | _           | 0      |      |        | ns   |      |

| TC Hold Time                  | t <sub>tch</sub>  | _           | 0      |      | _      | ns   |      |

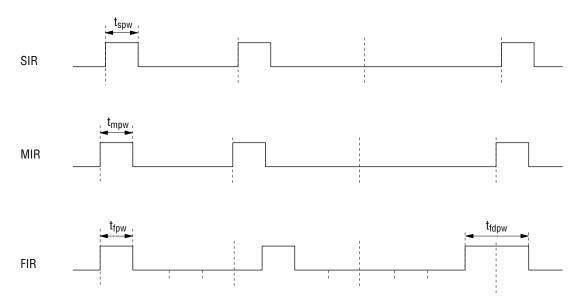

| CID Dulas Width               |                   | Transmitter | _      | 1.63 | _      | μs   |      |

| SIR Pulse Width               | t <sub>spw</sub>  | Receiver    | 0.9    |      | —      | μs   |      |

| CID Data Data Talaranaa       | SDRT              | Transmitter | —      |      | ±0.87  | %    |      |

| SIR Data Rate Tolerance       | וחעט              | Receiver    |        |      | ±2.0   | %    |      |

|                               |                   | Transmitter | _      | 218  | —      | ns   |      |

| MIR Pulse width               | t <sub>mpw</sub>  | Receiver    | 100    |      | —      | ns   |      |

| MID Data Data Talarapaa       | MDRT              | Transmitter | —      | —    | ±0.1   | %    |      |

| MIR Data Rate Tolerance       | IVIUNI            | Receiver    | _      |      | ±0.2   | %    |      |

| FID Cingle Dules Width        |                   | Transmitter | _      | 125  | —      | ns   |      |

| FIR Single Pulse Width        | t <sub>fpw</sub>  | Receiver    | 70     |      | 165    | ns   |      |

| EIP Data Pata Talaranaa       | FDRT              | Transmitter |        |      | ±0.01  | %    |      |

| FIR Data Rate Tolerance       | ΓUN I             | Receiver    | _      | _    | ±0.1   | %    |      |

| EID Double Dulce Width        | +                 | Transmitter |        | 250  |        | ns   |      |

| FIR Double Pulse Width        | t <sub>fdpw</sub> | Receiver    | 195    | _    | 285    | ns   |      |

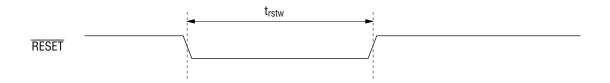

| Reset Pulse Width             | t <sub>rstw</sub> | _           | 70     |      | _      | ns   |      |

\*1 120 ns when crystal oscillation frequency = 18.432 MHz,

70 ns when crystal oscillation frequency = 48 MHz

\*2 That which occurs latest of the following is to be used for the data delay time  $(t_{rdd})$ : the change of the state of  $A_0$ - $A_3$ , the change from  $\overline{CS}$  high to low, and the change from  $\overline{RD}$  high to low.

\*3 That which occurs first of the following is to be used for the read data hold time  $(t_{rdh})$ : the change of the state of  $A_0$ - $A_2$ , the change from  $\overline{CS}$  low to high, and the change from SUNSTARE 7 RD for the high. Sunstare.com/ TEL: 0755-837/8810 FAX:0755-83376182 E-MAIL: szss200163.com

# • Read timing

## • Write timing

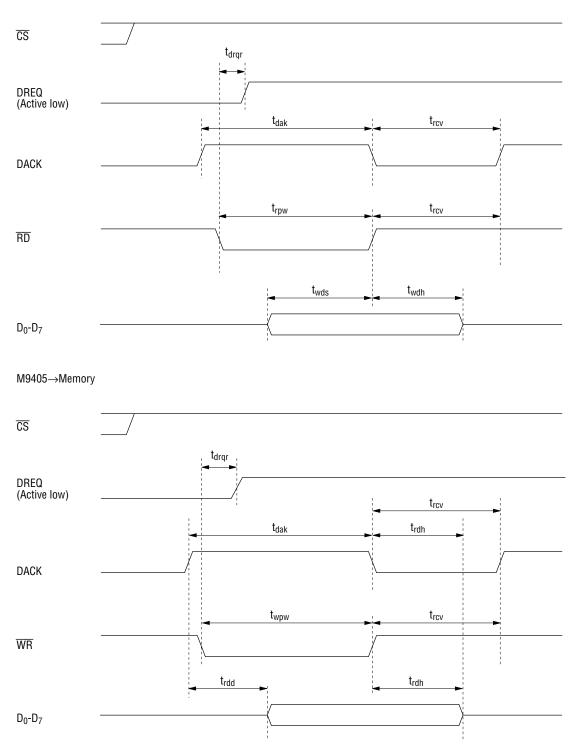

• DMAC access timing 1

$$\label{eq:def-DMA_EN} \begin{split} \mathsf{DMA}_{EN} &= "1", \ \mathsf{DMA}_{SL_1} = "0", \ \mathsf{DMA}_{SL_0} = "0" \\ \mathsf{Memory} &\rightarrow \mathsf{M9405} \end{split}$$

SUNSTAR电子元器件 http://www.sunstare.com/ TEL: 0755-83778810 FAX:0755-83376182 E-MAIL:szss20@163.com

## • DMAC access timing 2

$DMA\_EN = "1", DMA\_SL_1 = "0", DMA\_SL_0 = "1"$ M9405 $\rightarrow$ Memory

SUNSTAR电子元器件 http://www.sunstare.com/ TEL: 0755-83778810 FAX:0755-83376182 E-MAIL:szss20@163.com

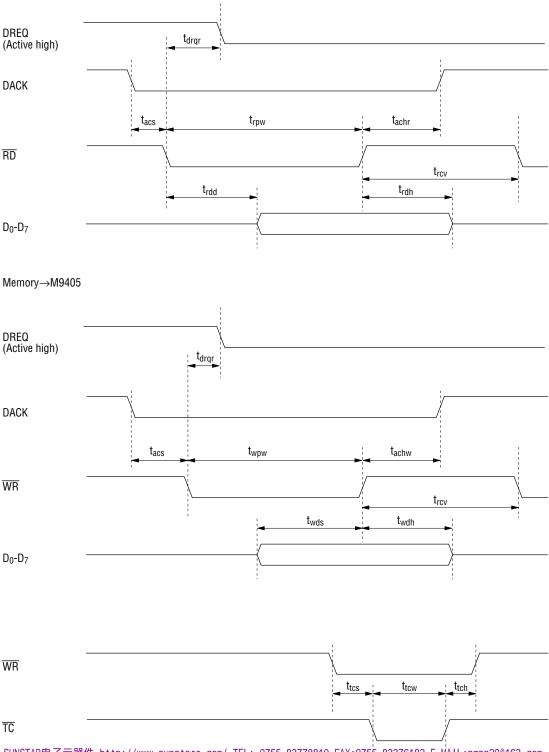

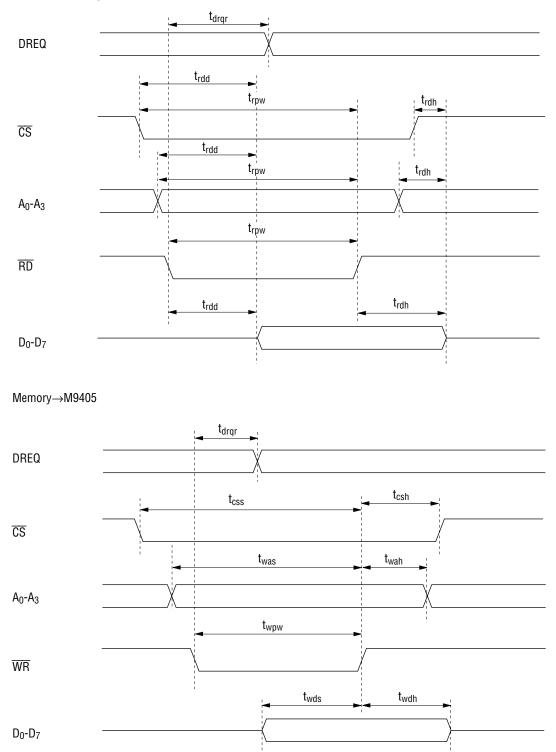

• DMAC access timing 3

DMA\_EN = "1", DMA\_SL<sub>1</sub> = "1", DMA\_SL<sub>0</sub> = "1" or "0" M9405→Memory

SUNSTAR电子元器件 http://www.sunstare.com/ TEL: 0755-83778810 FAX:0755-83376182 E-MAIL:szss20@163.com

## • Infrared interface timing

• Reset timing

# FUNCTIONAL DESCRIPTION

#### Modes

There are four modes provided by the MSM9405 for IrDA communication. Communication with IrDA1.0 is in SIR mode or Extended-SIR mode, while communication with IrDA1.1 is in MIR mode or FIR mode. In SIR mode, the MSM9405 has the necessary UART feature for IrDA communication. The Extended-SIR mode is an original feature of the MSM9405. In this mode, BOF/EOF insertion and CRC calculation/check are performed by the MSM9405. Therefore, the burden to the CPU can be reduced compared with IrDA1.0 communication using ordinary UART. Moreover, the Extended-SIR mode allows DMA transfer even in IrDA1.0 communication. In MIR mode, IrDA1.1 communication at up to 1.152 Mbps is possible. The FIR mode supports 4 Mbps transfer for IrDA1.1. Features of each mode are as follows:

| mode         | Transfer rate     | BOF | CRC | EOF | CE insertion/ | "0" insertion/ | Preamble          |

|--------------|-------------------|-----|-----|-----|---------------|----------------|-------------------|

| mode         | Transfer fale     | DUF |     |     | removal       | removal        | insertion/removal |

| SIR          | 2.4 to 115.2 kbps | SW  | SW  | SW  | SW            | —              | _                 |

| Extended-SIR | 2.4 to 115.2 kbps | HW  | HW  | HW  | HW            |                | _                 |

| MIR          | 0.576, 1.152 Mbps | HW  | HW  | HW  | _             | HW             | _                 |

| FIR          | 4 Mbps            | HW  | HW  | HW  | _             |                | HW                |

#### MSM9405 Modes Comparison

CE : Control Escape Byte SW : Software HW : Hardware

#### Sending/Receiving Switching Method

Mode switching between sending and receiving is made using the TX\_EN and RX\_EN bits in the ICR1 (Infrared Control Register 1). For sending, writing "1" in TX\_EN puts the MSM9405 in the sending mode. Writing "1" in RX\_EN puts the MSM9405 in the receiving mode. If "0" is written to both TX\_EN and RX\_EN bits, the MSM9405 does not perform sending/receiving but enters the idle state. Each register can be set even during the idle state. Data to be sent can be written in advance to the FIFO during the idle state.

If "1" is written to both TX\_EN and RX\_EN, the MSM9405 is put in the receiving mode.

#### **DMA Transfer**

The MSM9405 allows DMA transfer. The DMA transfer mode covers the single transfer mode and demand transfer mode, but not the block transfer mode. When a DMA controller with TC output is used for sending, the DMA controller and MSM9405 automatically perform high-speed transfer if the maximum frame length is specified for TFL and the transfer data length for the TC counter of the DMA controller.

The timing when the DREQ signal is asserted is as follows:

During receiving, DREQ is asserted when data in the FIFO is at or above the receiving threshold level or time-out occurs.

If all of the received data in the FIFO is read, DREQ is deasserted.

During sending, DREQ is asserted when data in the FIFO is lower than the sending threshold level. Sent data is written and DREQ is deasserted when the FIFO becomes full or TXE\_EV occurs.

## Time-out

The MSM9405 outputs an interrupt request or DMA request depending on the register setting when the following time-out occurs even if the received data is below the receiving threshold level:

The condition causing time-out in MIR or FIR mode is:

At least 1-byte data is in the receiving FIFO and  $69.5\,\mu$ s has passed after data is written from the receiving shift register to the FIFO. During this period, the CPU or DMA controller does not read the FIFO data.

The condition causing time-out in SIR or Extended SIR mode is:

At least 1-byte data is in the receiving FIFO and time (Tout) has passed after data is written from the receiving shift register to the FIFO. During this period, the CPU or DMA controller does not read the FIFO data.

Tout =  $4 \times 8 \times 1$ /baud rate

baud rate: Transfer rate (2.4 to 115.2 kbps)

#### **Register Map**

The MSM9405 contains 14 registers, of which 13 are available. Each register can be selected with the register address assigned from 0h through Ch. Various setting options are provided for each register to allow optimum communication.

| TT1 · · · · · · · · · · · · · · · · · · | 771 * ( ) 1 1 *       | •                       |

|-----------------------------------------|-----------------------|-------------------------|

| The registers are listed below.         | The register table is | given on the next page. |

| A <sub>3</sub> -A <sub>0</sub> | R/W | Register Nan | ne | Description                                                          |

|--------------------------------|-----|--------------|----|----------------------------------------------------------------------|

| 0h                             | R   | RDR          |    | Receive data register                                                |

| UII                            | W   | TDR          |    | Transmit data register                                               |

| 1h                             | R/W | ENR          |    | Interrupt enable register                                            |

| 2h                             | R   | EIR          |    | Interrupt event and status indication register                       |

| 3h                             | R   | LSR          |    | Status register                                                      |

| 4h                             | R/W | ICR1         |    | Transmit-receive control register                                    |

| 5h                             | R/W | ICR2         |    | BOF count setting register                                           |

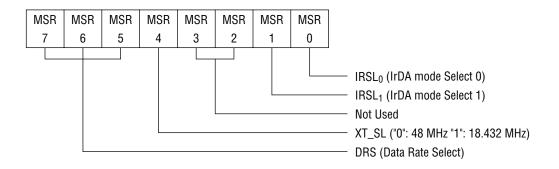

| 6h                             | R/W | MSR          |    | Register for setting a transfer mode and a data rate and selecting a |

|                                |     |              |    | crystal to be used                                                   |

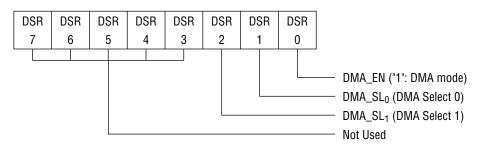

| 7h                             | R/W | DSR          |    | DMA mode setting register                                            |

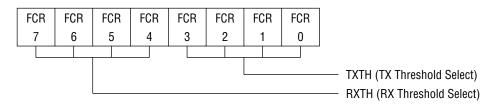

| 8h                             | R/W | FCR          |    | FIFO threshold setting register                                      |

| 9h                             | R/W | TFL (L)      | *1 | Transmit frame-length setting register (low-order byte)              |

| Ah                             | R/W | TFL (H)      | *1 | Transmit frame-length setting register (high-order byte)             |

| 9h                             | R   | TCC (L)      | *1 | Transmitter current-count register (low-order byte)                  |

| Ah                             | R   | TCC (H)      | *1 | Transmitter current-count register (high-order byte)                 |

| Bh                             | R/W | MDS (L)      | *2 | Maximum data size setting register (low-order byte)                  |

| 0h                             | R/W | MDS (H)      | *2 | Maximum data size setting register (high-order byte)                 |

| Bh                             | R   | RST (L)      | *2 | Receiver frame length stack register (low-order byte)                |

| Ch                             | R   | RST (H)      | *2 | Receiver frame length stack register (high-order byte)               |

| Fh                             | R/W | TEST         |    | Used for test.                                                       |

\*1 Whether TFL or TCC is read depends on the setting of the CTEST bit in the MSR register.

\*2 Whether MDS or RST is read depends on the setting of the CTEST bit in the MSR SUNSTAR电子玩算体研ttp://www.sunstare.com/ TEL: 0755-83778810 FAX:0755-83376182 E-MAIL:szss20@163.com

# SUNSTAR电子元器件 http://www.sunstare.com/ TEL: 0755-83376282 FAX:0755-83376182 E-MAIL:szss20@163.com OKI Semiconductor MSM9405

## **Register Table**

| A .1.1 | Register |               | DAM    |                   |                   | Fu                | unction           | of each l         | oit               |                   |                   |                  |

|--------|----------|---------------|--------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|

| Add    | name     | Mode          | R/W    | Bit7              | Bit6              | Bit5              | Bit4              | Bit3              | Bit2              | Bit1              | Bit0              |                  |

| 0      | םםם/חסד  |               |        | TDR <sub>7</sub>  | TDR <sub>6</sub>  | TDR <sub>5</sub>  | TDR <sub>4</sub>  | TDR <sub>3</sub>  | TDR <sub>2</sub>  | TDR <sub>1</sub>  | TDR <sub>0</sub>  |                  |

| 0      | TDR/RDR  | all           | R/W    | /RDR <sub>7</sub> | /RDR <sub>6</sub> | /RDR <sub>5</sub> | /RDR <sub>4</sub> | /RDR <sub>3</sub> | /RDR <sub>2</sub> | /RDR <sub>1</sub> | /RDR <sub>0</sub> |                  |

|        |          | SIR<br>Ex-SIR |        |                   |                   | RXH/T             | *                 |                   | *                 | -                 | FE_IE             |                  |

| 1      | ENR      | MIR           | R/W    | TXE_IE            | TXL_IE            |                   | EOF_IE            | MLE_IE            | CE_IE             | OE_IE             | AS_IE             |                  |

|        |          | FIR           |        |                   |                   | _IC               |                   |                   |                   |                   | ECE_IE            |                  |

|        |          | SIR           |        |                   |                   |                   | *                 |                   | *                 |                   |                   |                  |

|        |          | Ex-SIR        |        |                   |                   | RXH/T             |                   |                   |                   | -                 | FE_EV             |                  |

| 2      | EIR      | MIR           | R      | TXE_EV            | TXL_EV            | _EV               | EOF_EV            | MLE_EV            | CE_EV             | OE_EV             | AS_EV             |                  |

|        |          | FIR           |        |                   |                   |                   |                   |                   |                   |                   | ECE_EV            |                  |

|        |          | SIR           |        |                   |                   |                   |                   |                   |                   |                   |                   |                  |

|        | 1.05     | Ex-SIR        | -      |                   |                   |                   |                   |                   |                   |                   |                   |                  |

| 3      | LSR      | MIR           | R      | FLV <sub>5</sub>  | FLV <sub>4</sub>  | FLV <sub>3</sub>  | FLV <sub>2</sub>  | FLV <sub>1</sub>  | FLV <sub>0</sub>  | IR_DET            | TOUT              |                  |

|        |          | FIR           |        |                   |                   |                   |                   |                   |                   |                   |                   |                  |

|        |          | SIR           |        |                   |                   | *                 |                   | *                 | *                 |                   |                   |                  |

| 4      | ICR1     | Ex-SIR        | R/W    |                   |                   | CRC_              |                   |                   |                   |                   |                   |                  |

| 4      | IUNT     | MIR           |        | MS_EN             | TCC_EN            | INV               | FCLR              | IR_PLS            | S_EOT             | RX_EN             | TX_EN             |                  |

|        |          | FIR           |        |                   |                   |                   |                   | IN_FLO            |                   |                   |                   |                  |

|        |          | SIR           |        |                   |                   |                   |                   | *                 | *                 | *                 | *                 |                  |

| 5      | ICR2     | Ex-SIR        | R/W    |                   | CTEST             | SD_INV            | IRIN              | RXINV             | SBF <sub>3</sub>  | SBF <sub>2</sub>  | SBF <sub>1</sub>  | SBF <sub>0</sub> |

| J      | 10112    | MIR           | 11/ 11 | 01201             | 3D_111V           | _SL               |                   | MBF <sub>3</sub>  | MBF <sub>2</sub>  | MBF <sub>1</sub>  | MBF <sub>0</sub>  |                  |

|        |          | FIR           |        |                   |                   |                   |                   | *                 | *                 | *                 | *                 |                  |

| 6      | MSR      | all           | R/W    | DRS <sub>2</sub>  | DRS <sub>1</sub>  | DRS <sub>0</sub>  | XT_SL             | *                 | *                 | IRSL <sub>1</sub> | IRSL <sub>0</sub> |                  |

| 7      | DSR      | all           | R/W    | *                 | *                 | *                 | *                 | *                 | DMA_              | DMA_              | DMA_              |                  |

|        |          |               |        |                   |                   |                   |                   |                   | SL1               | SL <sub>0</sub>   | EN                |                  |

| 8      | FCR      | all           | R/W    | RXTH <sub>3</sub> | RXTH <sub>2</sub> | RXTH <sub>1</sub> | RXTH <sub>0</sub> | TXTH <sub>3</sub> | TXTH <sub>2</sub> | TXTH <sub>1</sub> | TXTH <sub>0</sub> |                  |

| 9      | TFL (L)  | all           | R/W    | TFL <sub>7</sub>  | TFL <sub>6</sub>  | TFL <sub>5</sub>  | TFL <sub>4</sub>  | TFL <sub>3</sub>  | TFL <sub>2</sub>  | TFL <sub>1</sub>  | TFL <sub>0</sub>  |                  |

|        | TCC (L)  | all           | R      | TCC7              | TCC <sub>6</sub>  | TCC <sub>5</sub>  | TCC <sub>4</sub>  | TCC <sub>3</sub>  | TCC <sub>2</sub>  | TCC <sub>1</sub>  | TCC <sub>0</sub>  |                  |

| А      | TFL (H)  | all           | R/W    | *                 | *                 | *                 | *                 | TFL <sub>11</sub> | TFL <sub>10</sub> | TFL <sub>9</sub>  | TFL <sub>8</sub>  |                  |

|        | TCC (H)  | all           | R      | *                 | *                 | *                 | *                 | TCC <sub>11</sub> | TCC <sub>10</sub> | TCC <sub>9</sub>  | TCC <sub>8</sub>  |                  |

| В      | MDS (L)  | all           | R/W    | MDS <sub>7</sub>  | MDS <sub>6</sub>  | MDS <sub>5</sub>  | MDS <sub>4</sub>  | MDS <sub>3</sub>  | MDS <sub>2</sub>  | MDS <sub>1</sub>  | MDS <sub>0</sub>  |                  |

|        | RST (L)  | all           | R      | RST <sub>7</sub>  | RST <sub>6</sub>  | RST <sub>5</sub>  | RST <sub>4</sub>  | RST <sub>3</sub>  | RST <sub>2</sub>  | RST <sub>1</sub>  | RST <sub>0</sub>  |                  |

| С      | MDS (H)  | all           | R/W    | *                 | *                 | *                 | *                 | MDS <sub>11</sub> | MDS <sub>10</sub> | MDS <sub>9</sub>  | MDS <sub>8</sub>  |                  |

|        | RST (H)  | all           | R      |                   |                   |                   |                   | RST <sub>11</sub> | RST <sub>10</sub> | RST <sub>9</sub>  | RST <sub>8</sub>  |                  |

| F      | TEST     | all           | R/W    | TEST <sub>7</sub> | TEST <sub>6</sub> | TEST <sub>5</sub> | TEST <sub>4</sub> | TEST <sub>3</sub> | TEST <sub>2</sub> | TEST <sub>1</sub> | TEST <sub>0</sub> |                  |

## Registers

• TDR: Transmit Data Register (Write Only) RDR: Receive Data Register (Read Only) (Address = 0h)

The TDR (Transmit Data Register) and RDR (Receive Data Register) are used to read/write data directly upon receiving/sending the data. The TDR and RDR share the same address. When data is written in the sending mode or during the idle state, the TDR works as the top of the FIFO and 1-byte data can be written to the FIFO. When data is read in the receiving mode, the RDR works as the bottom of the FIFO and 1-byte data in the FIFO can be read. Serial-to-parallel conversion is performed by the RSR. Parallel-to-serial conversion is performed by the TSR. Reading from the TDR or writing to the RDR is invalid. The contents of the FIFO and TDR/RDR are cleard by writing "1" to FCLR in the ICR1 register. The TSR and RSR cannot be cleared.

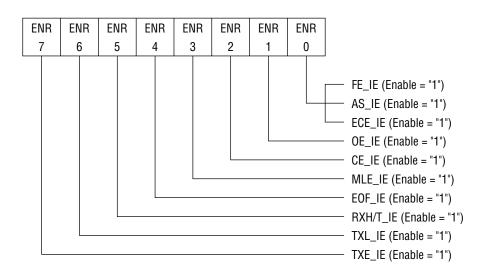

• ENR: Enable Register (Address = 1h)

The ENR (Enable Register) is used to control enabling/disabling various interrupts on the MSM9405. Each of eight bits corresponds to each of eight interrupts provided on the MSM9405. Each of eight interrupts can be independently controlled by each bit. When the system is reset, all bits are reset to "0". By writing "1" to the bit corresponding to the desired interrupt, the specified interrupt is enabled.

| ENR bit | Table bit                                                                                                                   |

|---------|-----------------------------------------------------------------------------------------------------------------------------|

|         | This bit works as FE_IE in SIR or Extended-SIR mode, as AS_IE in MIR mode, and as ECE_IE in FIR mode.                       |

|         | - FE_IE (Framing Error Interrupt Enable) (SIR mode/Extended-SIR mode): This bit enables/disables                            |

|         | interrupt when an FE (Framing Error : Stop bit not detected) has occurred.                                                  |

| ENR[0]  | - AS_IE (Abort Sequence Interrupt Enable) (MIR mode): This bit enables/disables interrupt when                              |

|         | an abort sequence has been received.                                                                                        |

|         | - ECE_IE (Encode Error Interrupt Enable) (FIR mode): This bit enables/disables interrupt when an encode error has occurred. |

|         | OE_IE (Overrun Error Interrupt Enable) : This bit enables/disables interrupt when an OE (Overrun                            |

| ENR[1]  | error : Error that occurs when the FIFO is full upon receiving and the next character is completely                         |

|         | received by the RSR) has occurred.                                                                                          |

|         | CE_IE (CRC Error Interrupt Enable) : This bit enables/disables interrupt when a CE (CRC Error) has                          |

| ENR[2]  | occurred. This bit is valid in either Extended-SIR, MIR, or FIR mode. In SIR mode, this bit must                            |

|         | be set to "0" (disable).                                                                                                    |

|         | MLE_IE (Maximum Length Error Interrupt Enable) : This bit enables/disables interrupt when an MLE                            |

| ENR[3]  | (Maximum Length Error: Error that occurs when a frame exceeding the maximum data size set by                                |

|         | the MDS is received) has occurred.                                                                                          |

|         | EOF_IE (End Of Frame Interrupt Enable) : This bit enables/disables interrupt when the last byte in                          |

| ENR[4]  | the frame's data field has been detected in either Extended-SIR, MIR, or FIR mode. In SIR mode,                             |

|         | this bit must be set to "0" (disable).                                                                                      |

| ENR[5]  | RXH/T_IE (Receiver High-Data-Level/Timeout Interrupt Enable) : This bit enables/disables interrupt                          |

|         | when the received data is at or above the receiving threshold level or time-out has occurred.                               |

| ENR[6]  | TXL_IE (Transmitter Low-Data-Level Interrupt Enable) : This bit enables/disables interrupt when the                         |

| 2111[0] | sent data is below the sending threshold level.                                                                             |

| ENR[7]  | TXE_IE (Transmitter Empty Interrupt Enable) : This bit enables/disables interrupt when both the                             |

| [,]     | FIFO and the TSR have become empty upon sending.                                                                            |

• EIR: Event Identification Register (Read Only) (Address = 2h)

The EIR (Event Identification Register) indicates factors of various interrupts on the MSM9405. Each of eight bits corresponds to each interrupt bit assignment set on the ENR. The EIR works as the status register even if the interrupt is disabled. When an event occurs, each corresponding bit is set to "1". When the system is reset, all bits are reset to "0".

| EIR |                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|-----|-----|-----|-----|-----|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |     |     |     |     |     |     |     | <ul> <li>FE_EV (Framing Error = "1")</li> <li>AS_EV (Abort Sequence = "1")</li> <li>ECE_EV (Encode Error = "1")</li> <li>OE_EV (Overrun Error = "1")</li> <li>CE_EV (CRC Error = "1")</li> <li>MLE_EV (Maximum Length = "1")</li> <li>EOF_EV (EOF = "1")</li> <li>RXH/T_EV (RX High-Data-Level/Timeout = "1")</li> <li>TXL_EV (TX Low-Data-Level = "1")</li> <li>TXE_EV (TX Empty = "1")</li> </ul> |

| EIR bit | Description                                                                                           |

|---------|-------------------------------------------------------------------------------------------------------|

|         | This bit works as FE_EV in SIR or Extended-SIR mode, as AS_EV in MIR mode, and as ECE_EV in           |

|         | FIR mode. When the CPU reads the EIR contents, this bit is set to "0".                                |

| EIR[0]  | - FE_EV (Framing Error Event) (SIR mode/Extended-SIR mode): The bit is set to "1" when FE occurs.     |

|         | - AS_EV (Abort Sequence Event) (MIR mode): The bit is set to "1" when an abort sequence is received.  |

|         | - ECE_EV (Encode Error Event) (FIR mode): The bit is set to "1" when ECE occurs.                      |

| EID[1]  | OE_EV (Overrun Error Event): When OE occurs, this bit is set to "1". When the CPU reads the EIR       |

| EIR[1]  | contents, OE_EV is set to "0". The RSR characters are not transferred to the FIFO but overwritten.    |

|         | CE_EV (CRC Error Event): When a CRC error occurs, this bit is set to "1". When the CPU reads the      |

| EIR[2]  | EIR, this bit is set to "0". This bit is valid in either Extended-SIR, MIR, or FIR mode.              |

|         | This bit is not used in SIR mode.                                                                     |

| EIR[3]  | MLE_EV (Maximum Length Error Event): When MLE occurs, this bit is set to "1". When the CPU            |

| [0]     | reads the EIR, this bit is set to "0".                                                                |

|         | EOF_EV (End Of Frame Event): This bit is valid in either Extended-SIR, MIR, or FIR mode. When the     |

| EIR[4]  | last byte in the frame's data field reaches the bottom of the FIFO in receiving mode, EOF_EV          |

|         | is set to "1". When the CPU reads the EIR, this bit is set to "0". In SIR mode, this bit is not used. |

|         | RXH/T_EV (Receiver High-Data-Level/Timeout Event): When received data in the FIFO is at or above      |

|         | the receiving threshold level or time-out occurs, RXH/T_EV is set to "1".                             |

|         | The condition for setting RXH/T_EV to "0" depends on the following two cases :                        |

| EIR[5]  | If received data in the FIFO is at or above the receiving threshold level : Received data is read.    |

|         | When received data in the FIFO is below the threshold level, this bit is set to "0".                  |

|         | If time-out occurs :                                                                                  |

|         | After received data in the FIFO is read, this bit is set to "0".                                      |

| EID (A) | TXL_EV (Transmitter Low-Data-Level Event): When sent data in the FIFO is below the sending            |

| EIR[6]  | threshold level, this bit is set to "1". When sent data is written and sent data in the FIFO is at or |

|         | above the threshold level, this bit is set to "0".                                                    |

| EIR[7]  | TXE_EV (Transmitter Empty Event): When both FIFO and TSR are empty in sending mode, this bit          |

|         | is set to "1". When the CPU reads the EIR, this bit is set to "0".                                    |

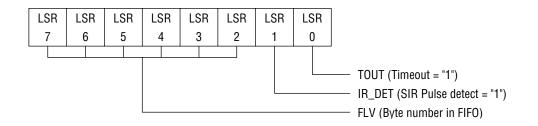

• LSR: Line Status Register (Read Only) (Address = 3h)

The LSR (Line Status Register) indicates various statuses of the MSM9405 that is running. When the system is reset, all bits of the LSR are set to "0". This register is for read only and cannot be written.

| LSR bit  | Description                                                                                                         |

|----------|---------------------------------------------------------------------------------------------------------------------|

|          | TOUT (FIFO Timeout): When time-out occurs in the FIFO during receiving, this bit is set to "1".                     |

| LSR[0]   | When received data is read from the FIFO, TOUT is set to "0".                                                       |

|          | IR_DET (SIR Pulse detect) : This bit is set to "1" when a pulse having a width of t <sub>spw</sub> (SIR pulse width |

| LSR[1]   | upon receiving). It is set to "0" when the CPU reads the LSR.                                                       |

| LSR[2-7] | FLV (FIFO Level): These bits indicate the number of data items in the FIFO with a value of 0 to 32.                 |

• ICR1: Infrared Control Register 1 (Address = 4h)

The ICR1 (Infrared Control Register 1) is used to set various environment so that the MSM9405 can perform IrDA communication under proper conditions. When the system is reset, all bits of ICR1 are set to "0".

| ICR1 |                                                                                                                                                                                                                                                                                                                                                            |

|------|------|------|------|------|------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |                                                                                                                                                                                                                                                                                                                                                            |

|      |      |      |      |      |      |      |      | <ul> <li>TX_EN ("1": Transmit Enable)</li> <li>RX_EN ("1": Receive Enable)</li> <li>S_EOT ("1": Set End Of Transmission)</li> <li>IR_PLS ("1": Send Interaction Pulse)</li> <li>FCLR ("1": FIFO Clear)</li> <li>CRC_INV ("1": Send Inverted CRC Enable)</li> <li>TCC_EN ("0": TCC off, "1": TCC on)</li> <li>MS_EN ("1": Automatic mode Select)</li> </ul> |

| ICR1 bit | Description                                                                                                                                                                        |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | TX_EN (Transmit Enable): When "1" is written to this bit, the sending mode is selected. When "0" is                                                                                |

| ICR1[0]  | written to this bit, sending terminates when data remaining in the FIFO has all been sent. In this                                                                                 |

|          | case, the TXE interrupt does not occur.                                                                                                                                            |

| ICR1[1]  | RX_EN (Receive Enable): When "1" is written to this bit, the receiving mode is selected. When "0" is                                                                               |

|          | written to this bit, the device enters receive end mode.                                                                                                                           |

|          | S_EOT (Set End Of Transmission): This bit is valid in Extended-SIR, MIR, or FIR mode. When "1" is                                                                                  |

|          | written to this bit, the data written to the FIFO next time is recognized as the end of frame, and                                                                                 |

| ICR1[2]  | immediately after it, the data added with CRC and EOF is sent as a frame. After a frame is sent,                                                                                   |

|          | this bit is automatically set to "0". To use S_EOT, TFL must be set to the maximum value or TCC                                                                                    |

|          | must be unused with TCC_EN = "0". This bit is not used in SIR mode.                                                                                                                |

|          | IR_PLS (Send Interaction Pulse): This bit is valid in MIR or FIR mode. When "1" is written to                                                                                      |

| ICR1[3]  | this bit, an approximately 2-µs serial infrared interaction pulse is sent immediately after the frame                                                                              |

| [0]      | being sent. After a frame is sent, this bit is automatically set to "0". This bit is not used in SIR                                                                               |

|          | mode and Extended-SIR mode.                                                                                                                                                        |

|          | FCLR (FIFO Clear): When "1" is written to this bit, the FIFO (including the TDR and RDR) is made                                                                                   |

| ICR1[4]  | empty. The FIFO threshold level does not change. The TSR and RSR are not cleared. When the                                                                                         |

|          | FIFO is made empty, this bit is automatically set to "0".                                                                                                                          |

|          | CRC_INV (Invert Transmitter CRC): This bit is valid in Extended-SIR, MIR, or FIR mode and is not                                                                                   |

| ICR1[5]  | used in SIR mode. When "1" is written to this bit, transmission is interrupted if TXE (Transmitter                                                                                 |

|          | Empty) occurs. The inverted CRC and EOF are automatically added to the frame that caused TXE,                                                                                      |

|          | then the frame is sent. Writing "0" to this bit disables this function.                                                                                                            |

|          | TCC_EN (TCC Enable): This bit is valid in Extended-SIR, MIR, or FIR mode. When this bit is set to                                                                                  |

| ICR1[6]  | "1", the TCC is enabled. When TCC_EN is set to "0", the TCC is disabled. To use S_EOT, the TFL must be set to the maximum value or the TCC must be disabled with TCC_EN0"          |

|          | must be set to the maximum value or the TCC must be disabled with TCC_EN = "0".<br>MS_EN (Mode Select Enable): When "1" is written to this bit, the MSM9405 performs the following |

|          | operation depending on the mode. After the operation is completed, this bit is automatically set to                                                                                |

|          | "0".                                                                                                                                                                               |

|          | If the MSM9405 is in FIR mode:                                                                                                                                                     |

|          | 1. The SD pin is set to "H", and the Tx pin to "H".                                                                                                                                |

| ICR1[7]  | 2. Approximately 300 ns later, the SD pin is set to "L".                                                                                                                           |

|          | 3. Approximately 300 ns later, the Tx pin is set to "L".                                                                                                                           |

|          | If the MSM9405 is in SIR, Extended-SIR, or MIR mode:                                                                                                                               |

|          | 1. The SD pin is set to "H", and the Tx pin to "L".                                                                                                                                |

|          | 2. Approximately 300 ns later, the SD pin is set to "L".                                                                                                                           |

|          | 3. The Tx pin is held in the "L" level for approximately 300 ns.                                                                                                                   |

• ICR2: Infrared Control Register 2 (Address = 5h)

The ICR2 (Infrared Control Register 2) is used to set various environment so that the MSM9405 can perform IrDA communication under proper conditions. When the system is reset, all bits of ICR2 are set to "0".

| ICR2 |                                                 |

|------|------|------|------|------|------|------|------|-------------------------------------------------|

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |                                                 |

|      |      |      |      |      |      |      |      |                                                 |

|      |      |      |      |      |      |      |      | SBF (SIR Beginning Flags)                       |

|      |      |      |      |      |      |      |      | MBF (MIR Beginning Flags)                       |

|      |      |      |      |      |      |      |      | — RXINV ("1": Signal Invert)                    |

|      |      |      |      |      |      |      |      | — IRIN_SL ("0": Single Input "1": Double Input) |

|      |      |      |      |      |      |      |      | SD_INV ("0": SD Active High "1": SD Active Low) |

|      |      |      |      |      |      |      |      | — CTEST ("0": TCC/RST "1": TFL/MDS)             |

| IRC2 bit  |                                                                                                                                                                                        |                     | Des                | cription                              |                                         |  |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|---------------------------------------|-----------------------------------------|--|--|--|--|

|           | These bits work as the SBF when Extended-SIR mode is selected, and as the MBF when the MIR                                                                                             |                     |                    |                                       |                                         |  |  |  |  |

|           | mode is selected. This function is disabled in SIR mode and FIR mode.                                                                                                                  |                     |                    |                                       |                                         |  |  |  |  |

|           | SBF (SIR beginning Flags): These bits determine the number of BOFs to be added during                                                                                                  |                     |                    |                                       |                                         |  |  |  |  |

|           | sending in Ex                                                                                                                                                                          | tended-SIR mod      | e as shown belo    | w.                                    |                                         |  |  |  |  |

|           | MBF (MIR Beginning Flags): These bits determine the number of BOFs to be added during                                                                                                  |                     |                    |                                       |                                         |  |  |  |  |

|           | sending in M                                                                                                                                                                           | IR mode as shov     | vn below.          |                                       |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | Encoding            | SIR BOFs           | MIR BOFs                              |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | 0000                | 1                  | 2                                     |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | 0001                | 2                  | 3                                     |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | 0010                | 3                  | 4                                     |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | 0011                | 4                  | 5                                     |                                         |  |  |  |  |

| ICR2[0-3] |                                                                                                                                                                                        | 0100                | 5                  | 8                                     |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | 0101                | 7                  | 12                                    |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | 0110                | 9                  | 16                                    |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | 0111                | 13                 | 24                                    |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | 1000                | 17                 | 24                                    |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | 1001                | 25                 | 24                                    |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | 1010                | 49                 | 24                                    |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | 1011                | 49                 | 24                                    |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | 1100                | 49                 | 24                                    |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | 1101                | 49                 | 24                                    |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | 1110                | 49                 | 24                                    |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | 1111                | 49                 | 24                                    |                                         |  |  |  |  |

|           | BXINV (IBIN                                                                                                                                                                            | Signal Invert). T   | his hit is used to | select active lov                     | v or active high of the receive signal. |  |  |  |  |

| ICR2[4]   | RXINV (""""                                                                                                                                                                            | - ,                 |                    |                                       | vor dotivo nigri or the roborvo orginal |  |  |  |  |

| 10112[1]  |                                                                                                                                                                                        |                     |                    |                                       |                                         |  |  |  |  |

|           | RXINV = "1": Active high<br>IRIN_SL (IRIN Select): This bit determines how the receive signal input pin is used.                                                                       |                     |                    |                                       |                                         |  |  |  |  |

|           | IRIN_SL (IRIN Select). This bit determines now the receive signal input pin is used.<br>IRIN_SL = "0": Only the input from the IRIN-A pin (2.4 kbps to 4 Mbps) is accepted.            |                     |                    |                                       |                                         |  |  |  |  |

| ICR2[5]   | IRIN_SL = 0. Only the input from the IRIN-A pin (2.4 kbps to 4 kbps) is accepted.<br>IRIN_SL = "1": An input from IRIN-A or IRIN-B is automatically selected depending on the transfer |                     |                    |                                       |                                         |  |  |  |  |

|           | rate. (A: 2.4 to 115.2 kbps, B: 0.576 to 4 Mbps)                                                                                                                                       |                     |                    |                                       |                                         |  |  |  |  |

|           |                                                                                                                                                                                        |                     |                    |                                       | re high/low) of the SD pin output on    |  |  |  |  |

|           | the MSM940                                                                                                                                                                             |                     |                    |                                       | g                                       |  |  |  |  |

| ICR2[6]   |                                                                                                                                                                                        | : Active high ("H   | " output durina s  | shutdown)                             |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | : Active low ("L"   |                    |                                       |                                         |  |  |  |  |

|           |                                                                                                                                                                                        | •                   |                    | · · · · · · · · · · · · · · · · · · · | L/TCC and MDS/RCC are read after        |  |  |  |  |

| ICR2[7]   |                                                                                                                                                                                        | to this bit, the TF | -                  |                                       |                                         |  |  |  |  |

• MSR: Mode Select Register (Address = 6h)

The MSR is used to select various modes of the MSM9405. When the system is reset, each bit is set to the initial value.

| MSR Bit  |                                     |                                                                                             | Des                                                                                                                | cription                                                                      |                                                                         |  |  |  |  |

|----------|-------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|

|          | IRSL (Infrared                      | IRSL (Infrared Mode Select): These bits are used to select the transfer mode as shown below |                                                                                                                    |                                                                               |                                                                         |  |  |  |  |

|          | The initial value                   | e is set to "00"                                                                            |                                                                                                                    |                                                                               |                                                                         |  |  |  |  |

|          |                                     | IRSL <sub>1</sub>                                                                           | IRSL <sub>0</sub>                                                                                                  | mode                                                                          |                                                                         |  |  |  |  |

|          |                                     | 0                                                                                           | 0                                                                                                                  | SIR                                                                           |                                                                         |  |  |  |  |

| MSR[0-1] |                                     | 0                                                                                           | 1                                                                                                                  | Extended-SIR                                                                  |                                                                         |  |  |  |  |

|          |                                     | 1                                                                                           | 0                                                                                                                  | MIR                                                                           |                                                                         |  |  |  |  |

|          | _                                   | 1                                                                                           | 1                                                                                                                  | FIR                                                                           |                                                                         |  |  |  |  |

| MSR[2-3] | These bits are r                    | not used.                                                                                   |                                                                                                                    |                                                                               |                                                                         |  |  |  |  |

|          | XT_SL (Crystal                      | Select): This                                                                               | bit determines th                                                                                                  | ne crystal to be used.                                                        |                                                                         |  |  |  |  |

|          | The initial value                   | e is set to "O".                                                                            |                                                                                                                    |                                                                               |                                                                         |  |  |  |  |

| MSR[4]   | XT_SL = "0": 48 MHz crystal is used |                                                                                             |                                                                                                                    |                                                                               |                                                                         |  |  |  |  |

| mont     | XT_SL = "0": 4                      | 8 MHz crystal                                                                               | is used                                                                                                            |                                                                               |                                                                         |  |  |  |  |

| mont     | XT_SL = "0": 4<br>XT_SL = "1": 1    | -                                                                                           |                                                                                                                    |                                                                               |                                                                         |  |  |  |  |

|          | XT_SL = "1": 1                      | 8.432 MHz cr                                                                                | ystal is used                                                                                                      | the transfer rate as sh                                                       | own below. The initial                                                  |  |  |  |  |

|          | XT_SL = "1": 1                      | 8.432 MHz cr                                                                                | ystal is used                                                                                                      | the transfer rate as sh                                                       | own below. The initial                                                  |  |  |  |  |

|          | XT_SL = "1": 1<br>DRS (Data Rate    | 8.432 MHz cr                                                                                | ystal is used                                                                                                      | the transfer rate as sh<br>MIR Data Rate                                      | own below. The initial<br>                                              |  |  |  |  |

|          | XT_SL = "1": 1<br>DRS (Data Rate    | 8.432 MHz cr<br>e Select): Thes                                                             | ystal is used<br>se bits determine                                                                                 |                                                                               |                                                                         |  |  |  |  |

|          | XT_SL = "1": 1<br>DRS (Data Rate    | 8.432 MHz cry<br>e Select): Thes<br>Encoding                                                | ystal is used<br>se bits determine<br>SIR Data Rate                                                                | MIR Data Rate                                                                 | FIR Data Rate                                                           |  |  |  |  |

| MSR[5-7] | XT_SL = "1": 1<br>DRS (Data Rate    | 8.432 MHz cm<br>e Select): Thes<br>Encoding<br>000                                          | ystal is used<br>se bits determine<br>SIR Data Rate<br>2400 bps                                                    | MIR Data Rate<br>0.576 Mbps                                                   | FIR Data Rate<br>reserved                                               |  |  |  |  |

|          | XT_SL = "1": 1<br>DRS (Data Rate    | 8.432 MHz cm<br>e Select): Thes<br>Encoding<br>000<br>001                                   | ystal is used<br>se bits determine<br>SIR Data Rate<br>2400 bps<br>9600 bps                                        | MIR Data Rate<br>0.576 Mbps<br>1.152 Mbps                                     | FIR Data Rate<br>reserved<br>4 Mbps                                     |  |  |  |  |

|          | XT_SL = "1": 1<br>DRS (Data Rate    | 8.432 MHz cm<br>e Select): Thes<br>Encoding<br>000<br>001<br>010                            | ystal is used<br>se bits determine<br>SIR Data Rate<br>2400 bps<br>9600 bps<br>19.2 kbps                           | MIR Data Rate<br>0.576 Mbps<br>1.152 Mbps<br>reserved                         | FIR Data Rate<br>reserved<br>4 Mbps<br>reserved                         |  |  |  |  |

|          | XT_SL = "1": 1<br>DRS (Data Rate    | 8.432 MHz cm<br>e Select): Thes<br>Encoding<br>000<br>001<br>010<br>011                     | ystal is used<br>se bits determine<br>SIR Data Rate<br>2400 bps<br>9600 bps<br>19.2 kbps<br>38.4 kbps              | MIR Data Rate<br>0.576 Mbps<br>1.152 Mbps<br>reserved<br>reserved             | FIR Data Rate<br>reserved<br>4 Mbps<br>reserved<br>reserved             |  |  |  |  |