This version: Jan. 1998 Previous version: Aug. 1996

# MSM82C54-2RS/GS/JS

# CMOS PROGRAMMABLE INTERVAL TIMER

# GENERAL DESCRIPTION

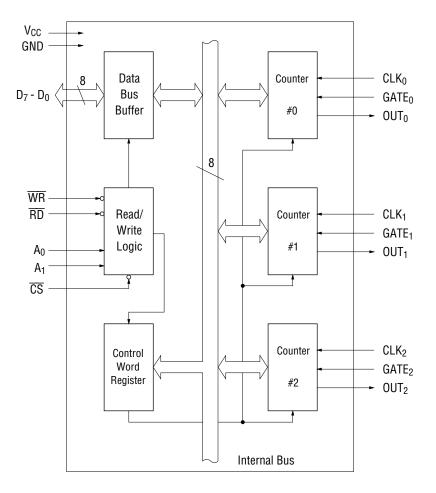

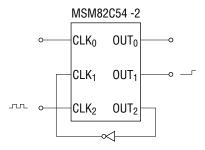

The MSM82C54-2RS/GS/JS is a programmable universal timer designed for use in microcomputer systems. Based on silicon gate CMOS technology, it requires a standby current of only 10  $\mu$ A (max.) when the chip is in the non-selected state. And during timer operation, the power consumption is still very low with only 10mA (max.) of current required.

It consists of three independent counters, and can count up to a maximum of 10 MHz. The timer features six different counter modes, and binary count/BCD count functions. Count values can be set in byte or word units, and all functions are freely programmable.

# FEATURES

- Maximum operating frequency of 10 MHz (V<sub>CC</sub>=5 V)

- High speed and low power consumption achieved by silicon gate CMOS technology

- Completely static operation

- Three independent 16-bit down-counters

- Status Read Back Command

- Six counter modes available for each counter

- Binary and decimal counting possible

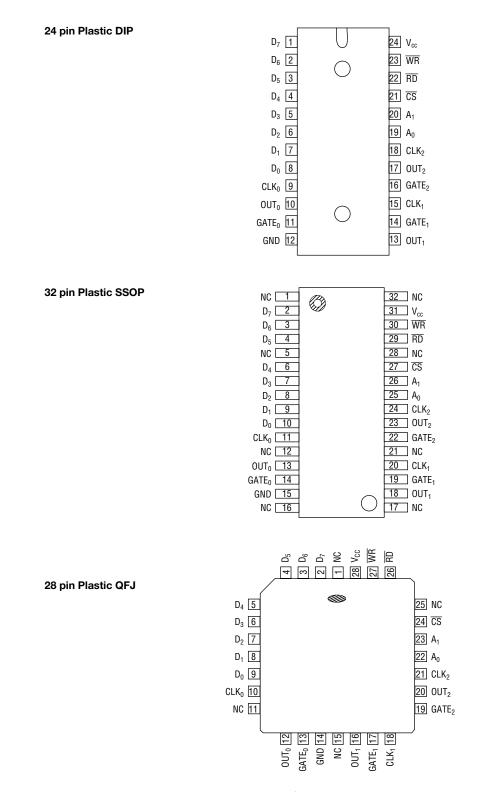

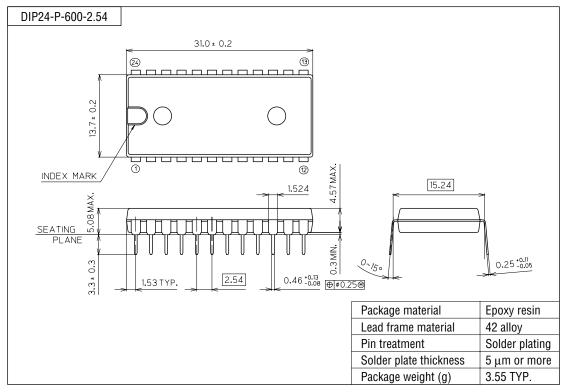

- 24-pin Plastic DIP (DIP24-P-600-2.54): (Product name: MSM82C54-2RS)

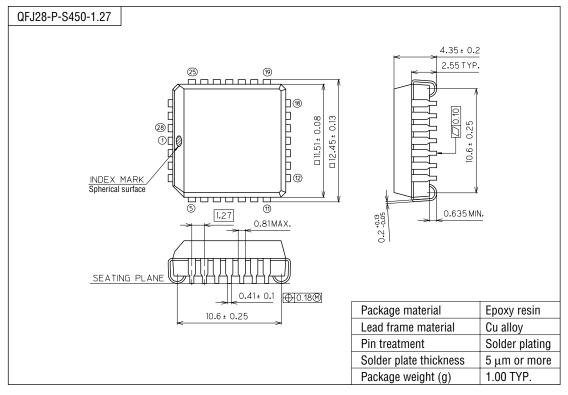

- 28-pin Plastic QFJ (QFJ28-P-S450-1.27): (Product name: MSM82C54-2JS)

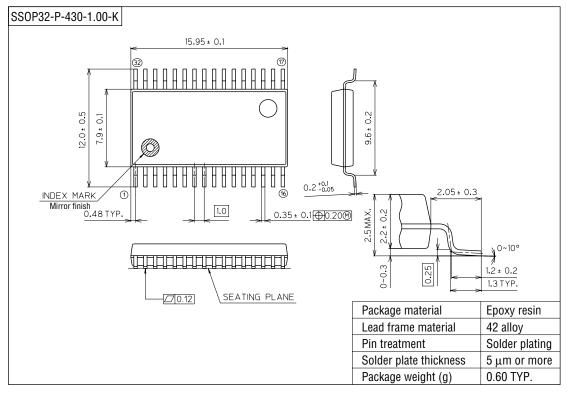

- 32-pin Plastic SSOP (SSOP32-P-430-1.00-K): (Product name: MSM82C54-2GS-K)

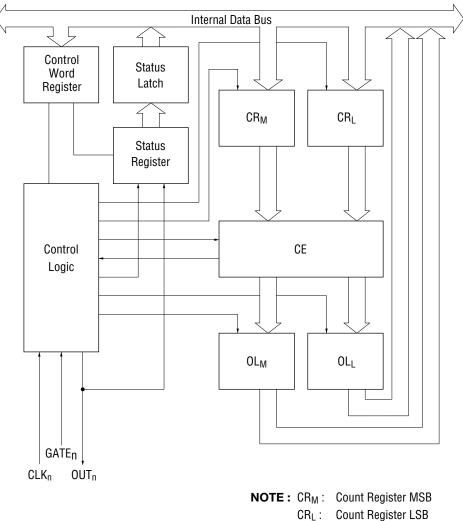

# FUNCTIONAL BLOCK DIAGRAM

MSM82C54-2RS/GS/JS

## **PIN CONFIGURATION (TOP VIEW)**

SUNSTAR电子元器件 http://www.sunstare.com/ TEL: 0755-83778810 [AC.denotes '395 connected"-MAIL:szss20@163.com

# ABSOLUTE MAXIMUM RATING

| Parameter            | Symbol                          | Condition      |                              | Rating       |              | Unit |

|----------------------|---------------------------------|----------------|------------------------------|--------------|--------------|------|

| Parameter            | Symbol                          | Condition      | MSM82C54-2RS                 | MSM82C54-2GS | MSM82C54-2JS | Unit |

| Power Supply Voltage | V <sub>CC</sub>                 | With           | -0.5 to +7                   |              |              |      |

| Input Voltage        | V <sub>IN</sub>                 | respect to GND |                              |              |              |      |

| Output Voltage       | V <sub>OUT</sub>                |                | -0.5 to V <sub>CC</sub> +0.5 |              |              | V    |

| Storage Temperature  | T <sub>STG</sub>                |                | — –55 to +150                |              | °C           |      |

| Power Dissipation    | Ta = $25^{\circ}$ C 0.9 0.7 0.9 |                |                              |              |              | W    |

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter             | Symbol          | Min. | Тур. | Max.                  | Unit |

|-----------------------|-----------------|------|------|-----------------------|------|

| Power Supply Voltage  | V <sub>CC</sub> | 4.5  | 5    | 5.5                   | V    |

| Operating Temperature | T <sub>op</sub> | -40  | +25  | +85                   | °C   |

| "L" Input Voltage     | VIL             | -0.5 |      | +0.8                  | V    |

| "H" Input Voltage     | VIH             | 2.2  | _    | V <sub>CC</sub> + 0.5 | V    |

# **DC CHARACTERISTICS**

| Parameter Symbol Conditions |                  |                                                                                                                                                    |                                              | Min.                 | Тур. | Max. | Unit |

|-----------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------|------|------|------|

| "L" Output Voltage          | V <sub>OL</sub>  | l <sub>0L</sub> = 2.5 mA                                                                                                                           |                                              | —                    | —    | 0.4  | V    |

| "H" Output Voltage          | V <sub>OH</sub>  | I <sub>0H</sub> = –2.5 mA                                                                                                                          |                                              | 3.0                  | —    | —    | V    |

| II Output voltage           | VOH              | I <sub>0H</sub> = −100 μA                                                                                                                          |                                              | V <sub>CC</sub> -0.4 | _    |      | V    |

| Input Leak Current          | ILI              | $0 \le V_{IN} \le V_{CC}$                                                                                                                          | V <sub>CC</sub> = 4.5 V to 5.5 V             | -10                  | —    | 10   | μA   |

| Output Leak Current         | ILO              | $0 \le V_{OUT} \le V_{CC}$                                                                                                                         | $Ta = -40^{\circ}C \text{ to } +85^{\circ}C$ | -10                  | —    | 10   | μA   |

| Standby Supply<br>Current   | I <sub>CCS</sub> | $\label{eq:cs_constraint} \begin{split} \overline{cs} &\geq V_{CC} - 0.2 \ V \\ V_{IH} &\geq V_{CC} - 0.2 \ V \\ V_{IH} &\leq 0.2 \ V \end{split}$ |                                              | _                    |      | 10   | μA   |

| Operating Supply<br>Curent  | I <sub>CC</sub>  | t <sub>CLK</sub> =100 ns, C <sub>L</sub> = 0 pF                                                                                                    |                                              |                      |      | 10   | mA   |

### **AC CHARACTERISTICS**

| $(V_{CC} = 4.5 \text{ V to } 5.5 \text{ V}, \text{ Ta} = -600000000000000000000000000000000000$ | 40°C to +85°C) |

|-------------------------------------------------------------------------------------------------|----------------|

|-------------------------------------------------------------------------------------------------|----------------|

|                                                                                          | <u> </u>         | 82C  | 54-2 |      | ,                       |

|------------------------------------------------------------------------------------------|------------------|------|------|------|-------------------------|

| Parameter                                                                                | Symbol           | Min. | Max. | Unit | Conditions              |

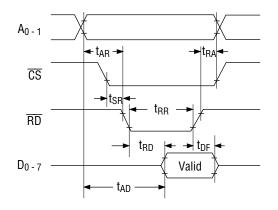

| Address Set-up Times to Falling Edge of RD                                               | t <sub>AR</sub>  | 30   | _    | ns   |                         |

| Chip Select Input Set-up Time to Falling Edge of RD                                      | t <sub>SR</sub>  | 0    | _    | ns   |                         |

| Address Hold Time from Rising Edge of RD                                                 | t <sub>RA</sub>  | 0    | _    | ns   | b                       |

| RD Pulse Width                                                                           | t <sub>RR</sub>  | 95   | _    | ns   | Read Timing             |

| Data Access Time from Falling Edge of RD                                                 | t <sub>RD</sub>  |      | 94   | ns   | ad T                    |

| Data Access Time after Address Determination                                             | t <sub>AD</sub>  | _    | 184  | ns   | Be                      |

| Delay Time from Rising Edge of $\overline{RD}$ to Data Floting State                     | t <sub>DF</sub>  | 5    | 65   | ns   |                         |

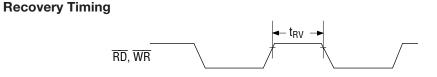

| RD Recovery Time                                                                         | t <sub>RV</sub>  | 165  | _    | ns   |                         |

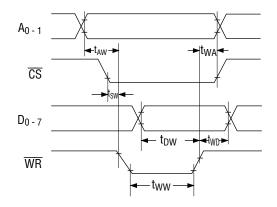

| Address Set-up Time to Falling Edge of WR                                                | t <sub>AW</sub>  | 0    | _    | ns   |                         |

| Chip Select Input Set-up Time to Falling Edge of WR                                      | tsw              | 0    | _    | ns   |                         |

| Address Hold Time from Rising Edge of WR                                                 | t <sub>WA</sub>  | 0    | _    | ns   | Write Timing            |

| WR Pulse Width                                                                           | t <sub>WW</sub>  | 95   | _    | ns   | Tin                     |

| Data Determination Set-up Time to Rising Edge of WR                                      | t <sub>DW</sub>  | 85   |      | ns   | Vrite                   |

| Data Hold Time after Rising Edge of WR                                                   | twp              | 0    | _    | ns   | -                       |

| WR Recovery Time                                                                         | trv              | 165  | _    | ns   |                         |

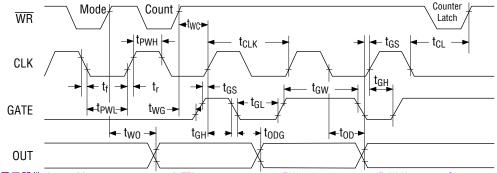

| CLK Cycle Time                                                                           | t <sub>CLK</sub> | 100  | D.C. | ns   | C <sub>L</sub> = 150 pF |

| CLK "H" Level Width                                                                      | t <sub>PWH</sub> | 30   | _    | ns   |                         |

| CLK "L" Level Width                                                                      | t <sub>PWL</sub> | 50   | _    | ns   |                         |

| CLK Rise Time                                                                            | tr               | _    | 25   | ns   |                         |

| CLK Fall Time                                                                            | t <sub>f</sub>   | _    | 25   | ns   |                         |

| GATE "H" Level Width                                                                     | t <sub>GW</sub>  | 50   | _    | ns   |                         |

| GATE "L" Level Width                                                                     | t <sub>GL</sub>  | 50   | _    | ns   |                         |

| GATE Input Set-up Time before Rising Edge of CLK                                         | t <sub>GS</sub>  | 40   | —    | ns   | ming                    |

| GATE Input Hold Time before Rising Edge of CLK                                           | t <sub>GH</sub>  | 50   |      | ns   | e Ti                    |

| Output Delay Time after Falling Edge of CLK                                              | t <sub>OD</sub>  | _    | 100  | ns   | Clock Gate Timing       |

| Output Delay Time after Falling Edge of GATE                                             | todg             | _    | 100  | ns   | lock                    |

| CLK Rise Delay Time after Rising Edge of $\overline{\text{WR}}$ for Count Value Loading  | t <sub>WC</sub>  | 0    | 55   | ns   | 0                       |

| GATE sampling delay time after rising edge of $\overline{\text{WR}}$ for count loading   | t <sub>WG</sub>  | -5   | 40   | ns   |                         |

| Output Delay Time after Falling Edge of WR for Mode Set                                  | t <sub>WO</sub>  | _    | 240  | ns   |                         |

| CLK Fall Set-up Time to Falling Edge of $\overline{\text{WR}}$ for Counter Latch Command | t <sub>CL</sub>  | -40  | 40   | ns   |                         |

Note: Timing measured at  $V_L = 0.8$  V and  $V_H = 2.2$  V for both inputs and outputs.

# **TIMING CHART**

### **WriteTiming**

### **Read Timing**

### **Clock & Gate Timing**

SUNSTAR电子元器件 http://www.sunstare.com/ TEL: 0755-83778810 FAX:0755-83376182 E-MAIL:szss20@163.com

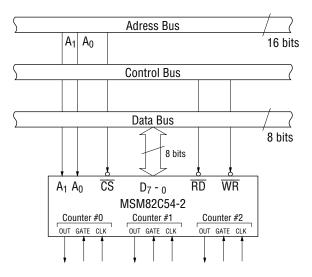

# DESCRIPTION OF PIN FUNCTIONS

| Pin Symbol                      | Name                      | Input/Output | Function                                                                                                                                                                                                                                                                  |

|---------------------------------|---------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>7</sub> - D <sub>0</sub> | Bidirectional<br>Data Bus | Input/Output | Three-state 8-bit bidirectional data bus used when writing control words and count value, and reading count values upon reception of $\overline{WR}$ and $\overline{RD}$ signals from CPU.                                                                                |

| <u>CS</u>                       | Chip Select<br>Input      | Input        | Data transfer with the CPU is enabled when this pin is at low level.<br>When at high level, the data bus ( $D_0$ thru $D_7$ ) is switched to high<br>impedance state where neither writing nor reading can be executed.<br>Internal registers, however, remain unchanged. |

| RD                              | Read Input                | Input        | Data can be transferred from MSM82C54-2 to CPU when this pin is at low level.                                                                                                                                                                                             |

| WR                              | Write Input               | Input        | Data can be transferred from CPU to MSM82C54-2 when this pin is at low level.                                                                                                                                                                                             |

| A <sub>0</sub> , A <sub>1</sub> | Address Input             | Input        | One of the three internal counters or the control word register is selected by $A_0/A_1$ combination. These two pins are normally connected to the two lower order bits of the address bus.                                                                               |

| CLK <sub>0</sub> - 2            | Clock Input               | Input        | Supply of three clock signals to the three counters incorporated in MSM82C54-2.                                                                                                                                                                                           |

| GATE <sub>0</sub> - 2           | Gate Input                | Input        | Control of starting, interruption, and restarting of counting in the three respective counters in accordance with the set control word contents.                                                                                                                          |

| OUT <sub>0</sub> - 2            | Counter Output            | Output       | Output of counter output wave form in accordance with the set mode and count value.                                                                                                                                                                                       |

### SYSTEM INTERFACING

# DESCRIPTION OF BASIC OPERATIONS

Data transfers between the internal registers and external data bus is outlined in the following table.

| CS | RD | WR | <b>A</b> 1 | A <sub>0</sub> | Function                                  |

|----|----|----|------------|----------------|-------------------------------------------|

| 0  | 1  | 0  | 0          | 0              | Data Bus to Counter #0 Writing            |

| 0  | 1  | 0  | 0          | 1              | Data Bus to Counter #1 Writing            |

| 0  | 1  | 0  | 1          | 0              | Data Bus to Counter #2 Writing            |

| 0  | 1  | 0  | 1          | 1              | Data Bus to Control Word Register Writing |

| 0  | 0  | 1  | 0          | 0              | Data Bus from Counter #0 Writing          |

| 0  | 0  | 1  | 0          | 1              | Data Bus from Counter #1 Writing          |

| 0  | 0  | 1  | 1          | 0              | Data Bus from Counter #2 Writing          |

| 0  | 0  | 1  | 1          | 1              |                                           |

| 1  | ×  | ×  | ×          | ×              | Data Bus in High Impedance Status         |

| 0  | 1  | 1  | ×          | ×              |                                           |

$\times\!\!:$  denotes "not specified"

# **DESCRIPTION OF OPERATION**

MSM82C54-2 functions are selected by control words from the CPU. In the required program sequence, the control word setting is followed by the count value setting and execution of the desired timer operation.

### **Control Word and Count Value Program**

Each counter operating mode is set by control word programming. The control word format is outlined below.

| D <sub>7</sub> | D <sub>6</sub> | $D_5$ | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|----------------|----------------|-------|----------------|----------------|----------------|----------------|----------------|

| SC1            | SC0            | RL1   | RL0            | M2             | M1             | MO             | BCD            |

| Select (       | Counter        | Read  | /Load          |                | Mode           | ]              | BCD            |

$<sup>(\</sup>overline{CS}=0, A_0, A_1=1, 1, \overline{RD}=1, \overline{WR}=0)$

| 0010 |     |                      |

|------|-----|----------------------|

| SC1  | SC0 | Set Contents         |

| 0    | 0   | Counter #0 selection |

| 0    | 1   | Counter #1 selection |

| 1    | 0   | Counter #2 selection |

| 1    | 1   | Read Back Command    |

### • Select Counter (SC0, SC1): Selection of set counter

### • Read/Load (RL1, RL0): Count value Reading/Loading format setting

| RL1 | RL0 | Set Contents                                    |

|-----|-----|-------------------------------------------------|

| 0   | 0   | Counter Latch Operation                         |

| 0   | 1   | Reading/Loading of Least Significant Byte (LSB) |

| 1   | 0   | Reading/Loading of Most Significant Byte (MSB)  |

| 1   | 1   | Reading/Loading of LSB followed by MSB          |

### • Mode (M2, M1, M0): Operation waveform mode setting

| M2 | M1 | MO | Set Contents                          |  |  |  |

|----|----|----|---------------------------------------|--|--|--|

| 0  | 0  | 0  | Mode 0 (Interruput on Terminal Count) |  |  |  |

| 0  | 0  | 1  | Mode 1 (Programmable One-Shot)        |  |  |  |

| ×  | 1  | 0  | Mode 2 (Rate Generator)               |  |  |  |

| ×  | 1  | 1  | Mode 3 (Square Wave Generator)        |  |  |  |

| 1  | 0  | 0  | Mode 4 (Software Triggered Strobe)    |  |  |  |

| 1  | 0  | 1  | Mode 5 (Hardware Triggered Strobe)    |  |  |  |

×: denotes "not specified"

### • **BCD:** Operation count mode setting

| BCD | Set Contents                              |

|-----|-------------------------------------------|

| 0   | Binary Count (16-bit Binary)              |

| 1   | BCD Count (4-decade Binary Coded Decimal) |

After setting Read/Load, Mode and BCD in each counter as outlined above, next set the desired count value. (In some Modes, the count value is set first. In next clock, loading is performed, then counting starts.) This count value setting must conform with the Read/Load format set in advance. Note that the internal counters are reset to 0000H during control word setting. The counter value (0000H) can't be read.

The program sequence of the MSM82C54-2 is flexible.

Free sequence programming is possible as long as the two following rules are observed:

- (i) Write the control word before writing the initial count value in each counter.

- (ii) Write the initial count value according to the count value read/write format specified by the control word.

- Note: Unlike the MSM82C53-2, the MSM82C54-2 allows count value setting for another counter between LSB and MSB settings.

### • Example of control word and count value setting

Counter #0: Read/Load LSB only, Mode 3, Binaty count, count value 3H Counter #1: Read/Load MSB only, Mode 5, Binaty count, count value AA00H Counter #2: Read/Load LSB and MSB, Mode 0, BCD count, count value 1234

| MVI A, 1EH<br>OUT n3                         | Counter #0 control word setting               |

|----------------------------------------------|-----------------------------------------------|

| MVI A, 6AH<br>OUT n3                         | Counter #1 control word setting               |

| MVI A, B1H<br>OUT n3                         | Counter #2 control word setting               |

| MVI A, 03H<br>OUT n0                         | Counter #0 count value setting                |

| MVI A, AAH<br>OUT n1                         | Counter #1 count value setting                |

| MVI A, 34H<br>OUT n2<br>MVI A, 12H<br>OUT n2 | Counter #2 count value setting (LSB then MSB) |

| _                                            |                                               |

Notes: n0: Counter #0 address n1: Counter #1 address n2: Counter #2 address n3: Control word register address

• The minimum and maximum count values which can be counted in each mode are listed below.

| Mode | Min. | Max. | Remarks                                        |

|------|------|------|------------------------------------------------|

| 0    | 1    | 0    | 0 executes 10000H count (ditto in other mdoes) |

| 1    | 1    | 0    | —                                              |

| 2    | 2    | 0    | 1 cannot be counted                            |

| 3    | 2    | 0    | 1 cannot be counted                            |

| 4    | 1    | 0    | _                                              |

| 5    | 1    | 0    | —                                              |

MSM82C54-2RS/GS/JS

### Internal Block Diagram of a Counter

- CE : Counter Element

- OLM: Output Latch MSB

- OLL: Output Latch LSB

### Mode definition

### Mode 0

- Application: Event counter

- Output operation: The output is set to "L" level by the control word setting, and kept at "L" level until the counter value becomes 0.

- Gate function: "H" level validates the count operation, and "L" level invalidates it. The gate does not affect the output.

- Count value load timing: after the control word and initial count value are written, the count value is loaded to the CE at the falling edge of the next clock pulse. The first clock pulse does not cause the count value to be decremented. In other words, if the initial count value is N, the output is not set to "H" level until the input of (N+1) the clock pulse after the initial count value writing.

- Count value writing during counting: The count value is loaded in the CE at the falling edge of the next clock, and counting with the new count value continues. The operation for 2-byte count is as follows:

- 1) The counting operation is suspended when the first byte is written. The output is immediately set to "L" level. (no clock pulse is required.)

- 2) After the second byte is written, the new count value is loaded to the CE at the falling edge of the next clock.

For the output to go to "H" level again, N+1 clock pulse are necessary after new count value N is written.

• Count value writing when the gate signal is "L" level:

The count value is also loaded to the CE at the falling edge of the next clock pulse in this case. When the gate signal is set to "H" level, the output is set to "H" level after the lapse of N clock pulses. Since the count value is already loaded in the CE, no clock pulse for loading in the CE is necessary.

## Mode 1

- Application: Digital one-shot

- Output operation: The output is set to "H" level by the control word setting. It is set to "L" level at the falling edge of the clock succeeding the gate trigger, and kept at "L" level until the counter value becomes 0. Once the output is set to "H" level, it is kept at "H" level until the clock pulse succeeding the next trigger pulse.

- Count value load timing: After the control word and initial count value are written, the count value is loaded to the CE at the falling edge of the clock pulse succeeding the gate trigger and set the output to "L" level. The one-shot pulse starts in this way. If the initial count value is N, the one-shot pulse interval equals N clock pulses. The one-shot pulse is not repetitive.

- Gate function: The gate signal setting to "L" level after the gate trigger does not affect the output. When it is set to "H" level again from "L" level, gate retriggering occurs, the CR count value is loaded again, and counting continues.

- Count value writing during counting It does not affect the one-shot pulse being counted until retriggering occurs.

### Mode 2

- Application: Rate generator, real-time interrupt clock.

- Output operation: The output is set to "H" level by control word setting. When the initial count value is decremented to 1, the output is set to "L" level during one clock pulse, and is then set to "H" level again. The initial count value is reloaded, and the above sequence repeats. In mode 2, the same sequence is repeated at intervals of N clock pulses if the initial count value is N for example.

- Gate function: "H" level validates counting, and "L" level invalidates it. If the gate signal is set to "L" level when the output pulse is "L" level, the output is immediately set to "H" level. At the falling edge of the clock pulse succeeding the trigger, the count value is reloaded and counting starts. The gate input can be used for counter synchronization in this way.

- Count value load timing: After the control word and initial count value is written, the count value is loaded to the CE at the falling edge of the next clock pulse. The output is set to "L" level upon lapse of N clock pulses after writing the initial count value N. Counter synchronization By software is possible in this way.

- Count value writing during counting:

Count value writing does not affect the current counting operation sequence. If new count value writing completes and the gate trigger arrives before the end of current counting operation, the count value is loaded to the CE at the falling edge of next clock pulse and counting continues from the new count value. If no gate trigger arrives, the new count value is loaded to the CE at the end of the current counting operation cycle. In mode 2, count value of 1 is prohibited.

## Mode 3

- Application: Baud rate generator, square wave generator

- Output operation: Same as mode 2 except that the output duty is different. The output is set to "H" level by control word setting. When the count becomes half the initial count value, the output is set to "L" level and kept at "L" level during the remainder of the count. Mode 3 repeats the above sequence periodically. If the initial count value is N, the output becomes a square wave with a period of N.

- Gate operation: "H" level validates counting, and "L" level invalidates it. If the gate signal is set to "L" level when the output is "L" level, the output is immediately set to "H" level. The initial count value is reloaded at the falling edge of the clock pulse succeeding the next gate trigger. The gate can be used for counter synchronization in this way.

- Count value load timing: After the control word and initial count value are written, the count value is loaded to the CE at the falling edge of the next clock pulse, Counter synchronization by software is possible in this way.

- Count value writing during counting: The count value writing does not affect the current counting operation. When the gate trigger input arrives before the end of a half cycle of the square wave after writing the new count value, the new count value is loaded in the CE at the falling edge of the next clock pulse, and counting continues using the new count value. If there is no gate trigger, the new count value is loaded at the end of the half cycle and counting continues.

- Even number counting operation:

The output is initially set to "H" level. The initial count value is loaded to the CE at the falling edge of the next clock pulse, and is decremented by 2 by consecutive clock pulses. When the scound water wate

• Odd number counting operation:

The output is initially set to "H" level. At the falling edge of the next clock pulse, the initial count value minus one is loaded in the CE, and then the value is decremented by 2 by consecutive clock pulses. When the counter value becomes 0, the output is set to "L" level, and then the initial count value minus 1 is reloaded to the CE. The value is then decremented by 2 by consecutive clock pulses. When the counter value becomes 2, the output is again set to "H" level and the initial count value minus 1 is again reloaded. The above operations are repeated. In other words, the output is set to "H" level during (N+1)/2 counting and to "L" level during (N-1)/2 counting in the case of odd number counting.

### Mode 4

- Application: Software trigger strobe

- Output operation: The output is initially set to "H" level. When the counter value becomes 0, the output goes to "L" level during one clock pulse, and then restores "H" level again.

- The count sequence starts when the initial count value is written.

- Gate function: "H" level validates counting, and "L" level invalidates counting. The gate signal does not affect the output.

- Count value load timing:

After the control word and initial count value are written, the count value is loaded to the CE at the falling edge of the next clock pulse. The clock pulse does not decrement the initial count value. If the initial count value is N, the strobe is not output unless N+1 clock pulses are input after the initial count value is written,

• Count value writing during counting:

The new count value is written to the CE at the falling edge of the next clock pulse, and counting continues using the new count value. The operation for 2-byte count is as follows: 1) First byte writing does not affect the counting operation.

2) After the second byte is written, the new count value is loaded to the CE at the falling edge of the next clock pulse.

This means that the counting operation is retriggered by software. The output strobe is set to "L" level upon input of N+1 clock pulses after the new count value N is written.

## Mode 5

- Application: Hardware trigger strobe

- Output operation:

The output is initially set to "H" level. When the counter value becomes 0 after triggering by the rising edge of the gate pulse, the output goes to "L" level during one clock pulse, and then restores "H" level.

• Count value load timing:

Even after the control word and initial count value are written, loading to the CE does not occur until the input of the clock pulse succeeding the trigger. For the clock pulse for CE loading, the count value is not decremented. If the initial count value is N, therefore, the output is not set to "L" level until N+1 clock pulses are input after triggering.

• Gate function:

The initial count value is loaded to the CE at the falling edge of the clock pulse succeeding gate triggering. The count sequence can be retriggered.

The gate pulse does not affect the output.

• Count value writing during counting:

The count value writing does not affect the current counting sequence. If the gate trigger is generated after the new count value is written and before the current counting ends, the new count value is loaded to the CE at the falling edge of the next clock pulse, and counting continues using the new count value. The various roles of the gate input signals in the above modes are summarized in the following table.

| Gate<br>Mode | "L" Level Falling Edge                                                                        | Rising Edge                                                      | "H" Level         |

|--------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------|

| 0            | Counting not possible                                                                         |                                                                  | Counting possible |

| 1            |                                                                                               | <ul><li>(1) Start of counting</li><li>(2) Retriggering</li></ul> |                   |

| 2            | <ol> <li>Counting not possible</li> <li>Counter output forced to "H" level</li> </ol>         | Start of counting                                                | Counting possible |

| 3            | <ol> <li>(1) Counting not possible</li> <li>(2) Counter output forced to "H" level</li> </ol> | Start of counting                                                | Counting possible |

| 4            | Counting not possible                                                                         |                                                                  | Counting possible |

| 5            |                                                                                               | <ul><li>(1) Start of counting</li><li>(2) Retriggering</li></ul> |                   |

SUNSTAR电子元器件 http://www.sunstare.com/ TEL: 0755-83376282 FAX:0755-83376182 E-MAIL:szss20@163.com

**OKI** Semiconductor

MSM82C54-2RS/GS/JS

Figures in these diagrams refer to counter values.

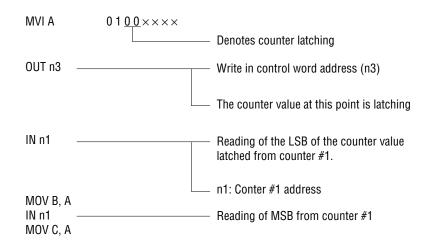

### **Reading Counter Values**

All MSM82C54-2 counting is down-counting, the counting being in steps of 2 in mode 3. Counter values can be read during counting by. (1) direct reading, (2) counter latching ("read on the fly"), and (3) read back command.

### (1) Direct reading

Counter values can be read by direct reading operations.

Since the counter value read according to the timing of the RD and CLK signals is not guaranteed, it is necessary to stop the counting by a gate input signal, or to interrupt the clock input temporarily by an external circuit to ensure that the counter value is correctly read.

### (2) Counter latching

In this method, the counter value is latched by writing counter latch command, thereby enabling a stable value to be read without effecting the counting in any way at all. The output latch (OL) of the selected counter latches the count value when a counter latch command is written. The count value is held until it is read by the CPU or the control word is set again.

If a counter latch command is written again before reading while a certain counter is latched, the second counter latch command is ignored and the value latched by the first counter latch command is maintained.

The MSM82C54-2 features independent reading and writing from and to the same counter. When a counter is programmed for the 2-byte counter value, the following sequence is possible:

- 1. Count value (LSB) reading

- 2. New count value (LSB) writing

- 3. Count value (MSB) reading

- 4. New count value (MSB) writing

An example of a counter latching program is given below.

Counter latching executed for counter #1 (Read/Load 2-byte setting)

### (3) Read Back Command Operation

Use of the read back command enables the user to check the count value, program mode, output pin state and null count flag of the selected counter.

The command is written in the control word register, and the format is as shown below. For this command, the counter selection occurs according to bits  $D_3$ ,  $D_2$  and  $D_1$ .

| D <sub>7</sub> | $D_6$ | $D_5$ | $D_4$  | $D_3$ | $D_2$ | D <sub>1</sub> | D <sub>0</sub> |

|----------------|-------|-------|--------|-------|-------|----------------|----------------|

| 1              | 1     | COUNT | STATUS | CNT2  | CNT1  | CNTO           | 0              |

(CS=0, A<sub>0</sub>, A<sub>1</sub>=1, RD=1, WR=0)

D<sub>5</sub>: 0 = Selected counter latch operation

D<sub>4</sub>: 0 = Selected counter status latch operation

D<sub>3</sub>: 1 = Counter #2 selection

D<sub>2</sub>: 1 = Counter #1 selection

D<sub>1</sub>: 1 = Counter #0 selection

D<sub>0</sub>: 0 Fixed

It is possible to latch multiple counters by using the read back command. Latching of a read counter is automatically canceled but other counters are kept latched. If multiple read back commands are written for the same counter, commands other than the first one are ignored. It is also possible to latch the status information of each counter by using the read back command. The status of a certain counter is read when the counter is read. The counter status format is as follows:

Bits  $D_5$  to  $D_0$  indicate the mode programmed by the most recently written control word. Bit  $D_7$  indicates the status of the output pin.

Use of this bit makes it possible to monitor the counter output, so the corresponding hardware may be omitted.

| $D_7$  | $D_6$         | $D_5$ | D <sub>4</sub> | $D_3$ | $D_2$ | D <sub>1</sub> | $D_0$ |  |

|--------|---------------|-------|----------------|-------|-------|----------------|-------|--|

| OUTPUT | NULL<br>COUNT | RL1   | RL0            | M2    | M1    | MO             | BCD   |  |

D<sub>7</sub>: 1 =Output pin status is 1.

0 = Output pin status is 0.

$D_6$ : 1 = Null count

0 = Count value reading is effective

D<sub>5</sub> - D<sub>0</sub>: Programmed mode of counter

(See the control word format.)

Null count indicates the count value finally written in the counter register (CR) has been loaded in the counter element (CE). The time when the count value was loaded in the CE depends on the mode of each counter, and it cannot be known by reading the counter value because the count value does not tell the new count value if the counter is latched. The null count operation is shown below.

| Operation                                        | Result           |

|--------------------------------------------------|------------------|

| A. Control word register writing                 | Null count = $1$ |

| B. Count register (CR) writing                   | Null count = $1$ |

| C. New count loading to CE (CR $\rightarrow$ CE) | Null count = $0$ |

Note: The null count operation for each counter is independent. When the 2-byte count is programmed, the null count is set to 1 when the count value of the second byte is written.

If status latching is carried out multiple times before status reading, other than the first status latch is ignored.

Simultaneous latching of the count and status of the selected counter is also possible. For this purpose, set bits  $D_4$  and  $D_3$ ,  $\overline{\text{COUNT}}$  and  $\overline{\text{STATUS}}$  bits, to 00. This is functionally the same as writing two separate read back commands at the same time. If counter/status latching is carried out multiple times before each reading, other than the first one is ignored here again. The example is shown below.

|    |                | C              | omi            | mai | nd             |                |                |                                        |       | nter 0      | Cour  | nter 1      | Cou   | nter 2 |

|----|----------------|----------------|----------------|-----|----------------|----------------|----------------|----------------------------------------|-------|-------------|-------|-------------|-------|--------|

| D7 | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D3  | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | Contents                               | Count | Status      | Count | Status      | Count | Status |

| 1  | 1              | 0              | 0              | 0   | 0              | 1              | 0              | Read back status and count (counter 0) | L     | L           | _     | _           | _     | _      |

| 1  | 1              | 1              | 0              | 0   | 1              | 0              | 0              | Read back status (counter 1)           | L     | L           | _     | L           | —     | _      |

| 1  | 1              | 1              | 0              | 1   | 1              | 0              | 0              | Read back status (counter 1 and 2)     | L     | L           | _     | L<br>(NOTE) | _     | L      |

| 1  | 1              | 0              | 1              | 1   | 0              | 0              | 0              | Read back status (counter 2)           | L     | L           | _     | L           | L     | L      |

| 1  | 1              | 0              | 0              | 0   | 1              | 0              | 0              | Read back status and count (counter 1) | L     | L           | L     | L<br>(NOTE) | L     | L      |

| 1  | 1              | 1              | 0              | 0   | 0              | 1              | 0              | Read back status (counter 0)           | L     | L<br>(NOTE) | L     | L           | L     | L      |

Note: The latch command at this time point is ignored, and the first latch command is valid.

If both the count and status are latched, the status latched in the first counter read operation is read. The order of count latching and status latching is irrelevant. The count(s) of the next one or two reading operations is or are read.

Note: There is the possibility of glitch noise in the output low level when reading out the data. Peak voltage in typical condition (5 V,  $25^{\circ}$ C) is approximately 1V and in the worst condition (5.5 V,  $-40^{\circ}$ C) is approximately 1.4V.

### **Example of Practical Application**

### • MSM82C54-2 used as a 32-bit counter.

Use counter #1 and counter #2

Counter #1: mode 0, upper order 16-bit counter value Counter #2: mode 2, lower order 16-bit counter value This setting enables counting up to a maximum of 2<sup>32</sup>.

MSM82C54-2RS/GS/JS

# PACKAGE DIMENSIONS

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

### MSM82C54-2RS/GS/JS

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

MSM82C54-2RS/GS/JS

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).