# **OKI** Semiconductor

# MSM6782-01

# **REAL TIME CLOCK**

#### **GENERAL DESCRIPTION**

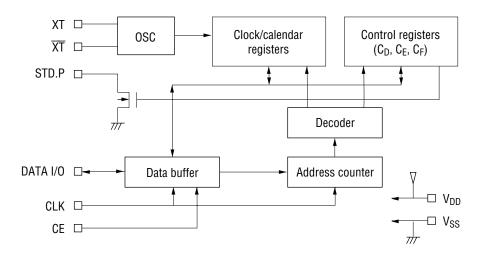

The MSM6782 - 01 is a CMOS Serial Interface Real Time Clock/Calendar.

The serial interface that can be controlled by mere 3 signal lines has minimized the number of CPU terminals required .

The MSM6782 - 01 provides 30-second adjustment, oscillation stop detection, and periodic flag setting and signal output in 4 different cycle periods.

The clock ranges are seconds, minutes, hours, days, months, years, and days of the week.

The interface supply voltage is 2.7V to 5.5V and the clock supply voltage is 2.0V to 5.5V.

The MSM6782 - 01 comes in an 8-pin DIP package or an 8-pin SOP package.

The MSM6782 - 01 is highly integrated and is suitable for use in a variety of portable applications.

#### **FEATURES**

- Real time clock providing seconds, minutes, hours, days, months, and days of the week.

- Serial interface controlled by 3 signal lines

- A periodic interrupt output in 4 different cycle periods (or periodic waveform output)

- Automatic leap year calendar

- 30-second adjustment controlled by software

- Stop and restart of clock

- Wide range of interface power supply: 2.7V to 5.5V

- Wide range of clock power supply: 2.0V to 5.5V

- 32.768kHz external quart crystal

- Low current consumption

- 8-pin plastic DIP (DIP8-P-300) (MSM6782-01RS)

- 8-pin plastic SOP (SOP8-P-250-K) (MSM6782-01MS-K)

# **BLOCK DIAGRAM**

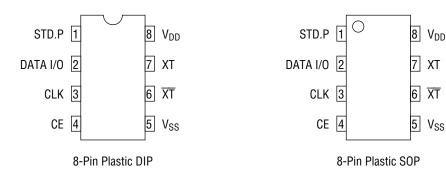

# **PIN CONFIGURATION**

Note: The actual type name is displayed as 6782-01.

Note: The actual type name is displayed as 82-01.

#### PIN DESCRIPTION

#### • STD.P (Pin No. 1)

Periodic output of N-CH OPEN DRAIN type or interrupt signal output of N-CH OPEN DRAIN type for the CPU. The periodic output is used to check the reference signal and oscillation frequency.

This pin is set as periodic output or interrupt signal output by writing "1" or "0" to the INT/STND bit.

This output is not inhibited by CE. For more information, see "FUNCTIONAL DESCRIPTION OF REGISTERS".

## • DATA I/O (Pin No.2)

Input/output pin for setting of WRITE mode or READ mode, writing of addresses, or writing/reading of data.

This pin is used as an input or output pin in high impedance state depending on whether WRITE mode or READ mode is selected in the first 8-bit data cycle after the rising of the CE input pulse.

#### • CLK (Pin No. 3)

Shift clock input pin. Data is taken in on the rising edge of a shift clock pulse when in WRITE mode and data is output when in READ mode.

#### • CE (Pin No. 4)

Chip enable input pin. "H" level on this pin means "enable".

When this pin is low, the DATA I/O pin goes into high impedance state, and DATA I/O and CLK are disabled inside the LSI and current stops flowing through those pins.

"L" level on this pin forces the TEST and REST bits of the  $C_F$  registers and the fr flag to be set to "0".

When turning the power ON, set this pin to "L" level.

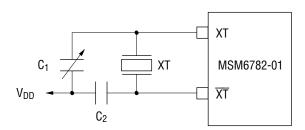

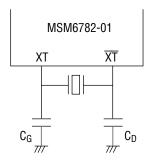

# • XT, $\overline{XT}$ (Pin Nos. 7 and 6)

32.768kHz crystal is to be connected to these pins.

When an external clock is used, it is to be input from XT, while  $\overline{\text{XT}}$  should be left open. The oscillation crystal and capacitors should be placed as close to the IC as possible. The oscillation circuit and other signal lines on any side of the LSI should be distant from each other.

## • V<sub>DD</sub>, V<sub>SS</sub> (Pin No.5)

Power supply pins.  $V_{DD}$  is used for positive supply and  $V_{SS}$  is for negative supply.

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter            | Symbol           | Condition | Rating                                       | Unit |

|----------------------|------------------|-----------|----------------------------------------------|------|

| Power supply voltage | V <sub>DD</sub>  |           | -0.3 to 7.0                                  |      |

| Input voltage        | VI               | Ta = 25°C | V <sub>ss</sub> -0.3 to V <sub>DD</sub> +0.3 | V    |

| Output voltage       | V <sub>0</sub>   |           | V <sub>ss</sub> -0.3 to V <sub>DD</sub> +0.3 |      |

| Storage temperature  | T <sub>STG</sub> | _         | -55 to +150                                  | °C   |

# RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol           | Condition | Rating     | Unit |

|-----------------------|------------------|-----------|------------|------|

| Power supply voltage  | V <sub>DD</sub>  | _         | 2.7 to 5.5 | V    |

| Clock power supply    | V <sub>CLK</sub> | _         | 2.0 to 5.5 | V    |

| Crystal frequency     | f <sub>X</sub>   | _         | 32.768     | kHz  |

| Operating temperature | T <sub>OP</sub>  | _         | -40 to +85 | °C   |

(Note) Clock power supply: Crystal oscillation and clock must be assured

# **ELECTRICAL CHARACTERISTICS**

## **DC Characteristics**

$(V_{DD} = 2.7 \text{ to } 5.5.V, Ta = -40 \text{ to } +85^{\circ}C)$

| Parameter              | Symbol            | Condition                       |                     | MIN                | TYP | мах         | Unit | Applicable terminal |

|------------------------|-------------------|---------------------------------|---------------------|--------------------|-----|-------------|------|---------------------|

| "H" Input Voltage      | V <sub>IH</sub>   | _                               |                     | 0.8V <sub>DD</sub> | _   | _           | V    | All input pins      |

| "L" Input Voltage      | V <sub>IL</sub>   |                                 |                     | _                  | _   | $0.2V_{DD}$ | V    | except XT           |

| "H" Input Current (1)  | I <sub>IH1</sub>  | $V_{I}=V_{DD}$                  |                     | _                  | _   | 1           | μΑ   | CE, CLK             |

| "L" Input Current (1)  | I <sub>IL1</sub>  | V <sub>I</sub> =V <sub>SS</sub> |                     | _                  | _   | -1          | μΑ   | CE, CLK             |

| "H" Input Current (2)  | I <sub>IH2</sub>  | V <sub>I</sub> =V <sub>DD</sub> |                     | _                  | _   | 10          | μΑ   | DATA I/O            |

| "L" Input Current (2)  | I <sub>IL2</sub>  | V <sub>I</sub> =V <sub>SS</sub> |                     | _                  | _   | -10         | μΑ   | DATA I/O            |

| "L" Output Current (1) | V <sub>OL1</sub>  | I <sub>0</sub> =1.0mA           |                     | _                  | _   | $0.2V_{DD}$ | V    | DATA I/O            |

| "H" Output Current     | V <sub>OH</sub>   | I <sub>0</sub> =-400μA          |                     | 0.8V <sub>DD</sub> | _   | _           | V    | DATA I/O            |

| "L" Output Current (2) | V <sub>OL2</sub>  | I <sub>0</sub> =1.0mA           |                     | _                  | _   | $0.2V_{DD}$ | V    | STD.P               |

| OFF Leak Current       | V <sub>OFLK</sub> | V <sub>0</sub> =V <sub>DD</sub> |                     | _                  | _   | 10.0        | μΑ   | STD.P               |

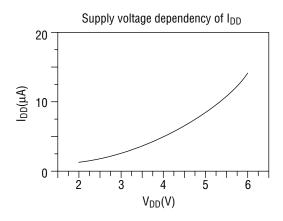

| Current Consumption(1) | V <sub>DD1</sub>  | f <sub>X</sub> =32.768kHz       | V <sub>DD</sub> =5V | _                  | _   | 20.0        | μΑ   | V <sub>DD</sub>     |

| Current Consumption(2) | V <sub>DD2</sub>  | V <sub>I</sub> (CE)=0V          | V <sub>DD</sub> =2V | _                  | _   | 2.5         | μА   | V <sub>DD</sub>     |

# • AC Characteristics

$(V_{DD} = 2.7 \text{ to } 5.5V, Ta = -40 \text{ to } +85^{\circ}C)$

|                           |                  |                       | (*01 |     | 0.0 v, .u | 10 10 100 0) |

|---------------------------|------------------|-----------------------|------|-----|-----------|--------------|

| Parameter                 | Symbol           | Condition             | MIN  | TYP | MAX       | Unit         |

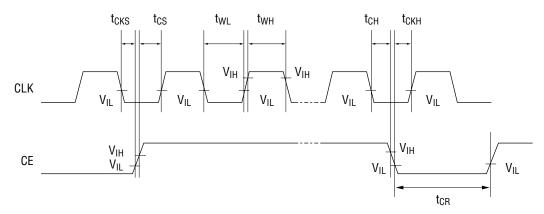

| CLK "H" Pulse Width       | t <sub>WH</sub>  | _                     | 300  | _   | _         | ns           |

| CLK "L" Pulse Width       | twL              | _                     | 300  | _   | _         | ns           |

| CE Setup Time             | t <sub>CS</sub>  | _                     | 150  | _   |           | ns           |

| CE Hold Time              | t <sub>CH</sub>  | _                     | 200  | _   | _         | ns           |

| CE Recovery Time          | t <sub>CR</sub>  | _                     | 300  | _   | _         | ns           |

| CLK Setup Time            | t <sub>CKS</sub> | _                     | 20   | _   | _         | ns           |

| CLK Hold Time             | t <sub>CKH</sub> | _                     | 20   | _   | _         | ns           |

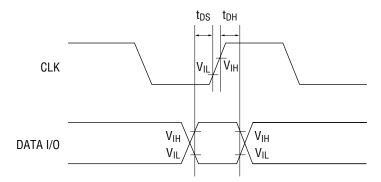

| WRITE Data Setup Time     | t <sub>DS</sub>  | _                     | 50   | _   | _         | ns           |

| WRITE Data Hold Time      | t <sub>DH</sub>  | _                     | 50   | _   | _         | ns           |

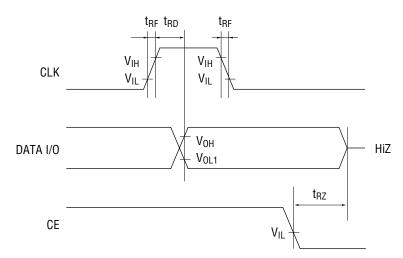

| READ Data Delay Time      | t <sub>RD</sub>  | C <sub>L</sub> = 50pF | _    | _   | 250       | ns           |

| Output Disable Delay Time | t <sub>RZ</sub>  | _                     | _    | _   | 100       | ns           |

| Input Rise, Fall Time     | t <sub>RF</sub>  | _                     | _    | -   | 20        | ns           |

(Note) See Timing Chart.

# **TIMING CHART**

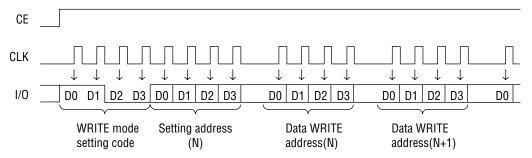

# **WRITE** mode

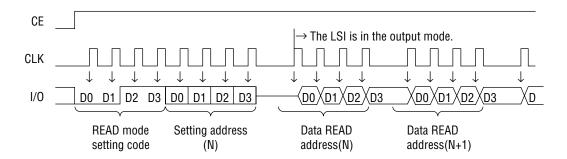

## **READ** mode

#### **FUNCTIONAL DESCRIPTION**

#### **REGISTER TABLE**

| HEX | A3A2A1A0 | Register name    | D3<br>(MSB)     | D2               | D1               | D0<br>(LSB)      | Count range | Note                     |

|-----|----------|------------------|-----------------|------------------|------------------|------------------|-------------|--------------------------|

| 0   | 0 0 0 0  | S <sub>1</sub>   | S <sub>8</sub>  | S <sub>4</sub>   | S <sub>2</sub>   | S <sub>1</sub>   | 0 to 9      | 1-second digit register  |

| 1   | 0 0 0 1  | S <sub>10</sub>  | f <sub>0</sub>  | S <sub>40</sub>  | S <sub>20</sub>  | S <sub>10</sub>  | 0 to 5      | 10-second digit register |

| 2   | 0 0 1 0  | $MI_1$           | mi <sub>8</sub> | mi <sub>4</sub>  | mi <sub>2</sub>  | mi <sub>1</sub>  | 0 to 9      | 1-minute digit register  |

| 3   | 0 0 1 1  | MI <sub>10</sub> | f <sub>r</sub>  | mi <sub>40</sub> | mi <sub>20</sub> | mi <sub>10</sub> | 0 to 5      | 10-minute digit register |

| 4   | 0 1 0 0  | H <sub>1</sub>   | h <sub>8</sub>  | h <sub>4</sub>   | h <sub>2</sub>   | h <sub>1</sub>   | 0 to 9      | 1-hour digit register    |

| 5   | 0 1 0 1  | H <sub>10</sub>  | f <sub>r</sub>  | PM/AM            | h <sub>20</sub>  | h <sub>10</sub>  | 0 to 1, 2   | 10-hour digit register   |

| 6   | 0 1 1 0  | D <sub>1</sub>   | d <sub>8</sub>  | d <sub>4</sub>   | d <sub>2</sub>   | d <sub>1</sub>   | 0 to 9      | 1-day digit register     |

| 7   | 0 1 1 1  | D <sub>10</sub>  | f <sub>r</sub>  | *                | d <sub>20</sub>  | d <sub>10</sub>  | 0 to 3      | 10-day digit register    |

| 8   | 1 0 0 0  | MO <sub>1</sub>  | mo <sub>8</sub> | mo <sub>4</sub>  | mo <sub>2</sub>  | mo <sub>1</sub>  | 0 to 9      | 1-month digit register   |

| 9   | 1 0 0 1  | MO <sub>10</sub> | f <sub>r</sub>  | *                | *                | mo <sub>10</sub> | 0 to 1      | 10-month digit register  |

| Α   | 1 0 1 0  | Y <sub>1</sub>   | У8              | У4               | У2               | У1               | 0 to 9      | 1-year digit register    |

| В   | 1 0 1 1  | Y <sub>10</sub>  | У80             | У40              | У20              | У10              | 0 to 9      | 10-year digit register   |

| C   | 1 1 0 0  | W                | f <sub>r</sub>  | W4               | W2               | W1               | 0 to 6      | Week digit register      |

| D   | 1 1 0 1  | C <sub>D</sub>   | 30-secADJ       | IRQ-F            | CAL/HW           | HOLD             | _           | Control register D       |

| Е   | 1 1 1 0  | CE               | t <sub>1</sub>  | t <sub>0</sub>   | INT/STND         | MASK             | _           | Control register E       |

| F   | 1 1 1 1  | C <sub>F</sub>   | TEST            | 24/12            | ST0P             | REST             | _           | Control register F       |

- The relation between the register's bit 0 and bit 1 is logically positive as 0="L" and 1="H".

- The counted values are in BCD notation. For example, with 1-year register  $(Y_1)$ ,  $(y_8, y_4, y_2, y_1) = (0, 0, 1, 0)$  means the last digit ("2") of

- Bit \* also can be used as RAM.

"1992".

- It is unexecutable to write data into the IRQ-F bit.

- The IRQ-F bit is set to "1" when a specified carry determined by the combination of  $t_1$  and  $t_0$  is executed.

- The IRQ-F bit holds "1" until the reading of  $C_D$  is complete and is reset to "0" automatically after the reading of  $C_D$  is complete.

- The bit fo (OSC FLAG) memorizes that oscillation stops.

- This bit is used to monitor the battery.

- This bit is cleared by writing a "0". (A "1" also can be written into this bit.)

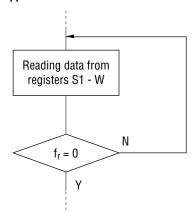

- The bit f<sub>r</sub> (READ FLAG) goes "0" when the CE pin is set at "L" level and goes "1" when a carry occurs for 1-second digit while the CE input is at "H" level.

- Thus, it is possible to judge whether a carry occurs for 1-second digit during the reading of the clock register (CE input = "H").

- If the bit  $f_r$  is set at "1", it is required to read the clock register once more.

- The "1" of the PM/AM bit indicates PM and its "0" indicates AM.

#### **FUNCTIONAL DESCRIPTION OF REGISTERS**

Registers S<sub>1</sub>, S<sub>10</sub>, MI<sub>1</sub>, MI<sub>10</sub>, H<sub>1</sub>, H<sub>10</sub>, D<sub>1</sub>, D<sub>10</sub>, MO<sub>1</sub>, MO<sub>10</sub>, Y<sub>1</sub>, Y<sub>10</sub>, W

• These are abbreviations for Second<sub>1</sub>, Second<sub>10</sub>, MInute<sub>1</sub>, MInute<sub>10</sub>, Hour<sub>1</sub>, Hour<sub>10</sub>, Day<sub>1</sub>, Day<sub>10</sub>, MOnth<sub>1</sub>, MOnth<sub>10</sub>, Year<sub>1</sub>, Year<sub>10</sub>, Week.

These values are in BCD notation.

• Refer to the REGISTER TABLE for more detalied information.

All registers are logically positive.

For example,  $(S_8, S_4, S_2, S_1) = 1001$  means 9 seconds.

The \* bit in the register table is writable/readable and can be used as RAM.

- Writing non-existant data may cause a clocking error.

- PM/AM, h<sub>20</sub>, h<sub>10</sub>

- a) In 12-hour mode

The existant time is AM 12:00 through AM 11:00 and PM 12:00 through PM 11:00. It is impossible to write data into the  $h_{20}$  bit which is fixed to "0" unconditionally. The  $h_{20}$  bit is not set by clocking.

b) In 24-hour mode

The existant time is 0:00 clock through 23:00 clock.

The PM/AM bit written is ignored and read out as "0" unconditionally.

• Registers Y<sub>1</sub>, Y<sub>10</sub>, and Leap Year

When using the Christian Era calendar,  $Y_1$  and  $Y_{10}$  are assigned to the last 2 digits of the year of Christian Era.

The MSM6782 - 01 is capable of automatically identifying a leap year when the last 2-digit number of the year can be divided by four. The last 2-digit number 99 changes to 00 next year.

Register W

The count range of the register W is  $0 \sim 6$ . The following table shows a possible bit data definition.

| W <sub>4</sub> | W <sub>2</sub> | W <sub>1</sub> | Day of Week |

|----------------|----------------|----------------|-------------|

| 0              | 0              | 0              | Sunday      |

| 0              | 0              | 1              | Monday      |

| 0              | 1              | 0              | Tuesday     |

| 0              | 1              | 1              | Wednesday   |

| 1              | 0              | 0              | Thursday    |

| 1              | 0              | 1              | Friday      |

| 1              | 1              | 0              | Saturday    |

#### f<sub>0</sub> Flag

The  $f_0$  flag bit memorizes that oscillation stops and is used to monitor the output of the battery. The "1" of this bit indicates stop of oscillation. This bit is cleared by writing "0". It is not permitted to write "1" into this bit.

#### f<sub>r</sub> Flag

The  $f_r$  flag bit indicates a carry when the CE input is at "H" level.

This bit is checked when the clock/calendar registers are read out. If this bit is set to "1", it is possible to read out these registers without using the HOLD bit.

This bit is cleared by setting the CE input to "L" level.

# C<sub>D</sub> REGISTER (Control D Register)

## • 30-sec ADJ (30-second adjustment bit)

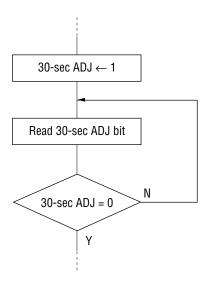

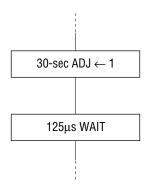

When writing to this bit, if the second digits are smaller than 30, the second digits are reset to 00, and if it is larger than 30, the second digits are reset to 00 and a carry into the minute digit is executed. Data can not be written into the  $S_1 \sim W$  registers and a "1" can not be written into the REST bit of the  $C_F$  register 125 $\mu$ s after writing into this bit because internal processing is being executed. This bit holds "1" 125 $\mu$ s after writing, and returns to "0" automatically. Therefore, data should be written into the  $S_1 \sim W$  registers after checking that this bit has returned to "0".

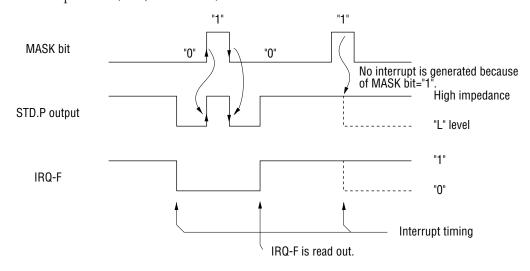

#### IRO - F

This bit is set to "1" and the STD.P output goes low in the cycle period specified by the combination of bit  $t_1$  and bit  $t_0$  of the  $C_E$  register. If INT/STND = "1", the bit status "1" and output level "L" are kept until reading of the  $C_D$  register is complete.

After the  $C_D$  register is read out, the IRQ - F bit returns to "0" and the STD.P output goes into high impedance automatically.

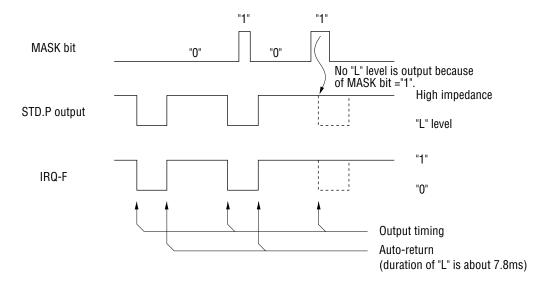

If INT/STD = "0", the IRQ -F bit returns to "0" about 7.8 ms later or immediately after the  $C_D$  register is read out, and the STD.P returns to "high impedance" about 7.8 ms later.

## • CAL/HW (Clock range switching bit)

CAL/HW = "1": Seconds, minutes, hours, days, month, year, day of week

CAL/HW = "0": Seconds, minutes, hours, day of week

If this bit is "0", the  $D_1$ ,  $D_{10}$ ,  $MO_1$ ,  $MO_{10}$ ,  $Y_1$ ,  $Y_{10}$  registers can be used as 4-bit data RAM and the \* bits and  $f_r$  bits of the  $D_{10}$  and  $MO_{10}$  registers also can be used as independent RAM, because these registers stop clock operation.

#### HOLD

"1" of this bit inhibits a carry into 1-second digit.

Clock operation continues before reaching a second.

During Hold = "1", if a carry occurs, the S1 counter is incremented by 1 second after Hold = "0".

This bit is cleared to zero by writing "0".

## C<sub>E</sub> REGISTER (Control E Register)

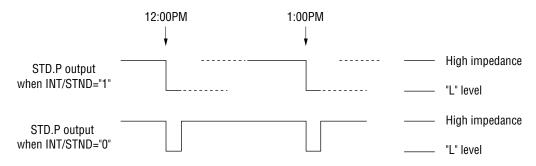

•  $t_1, t_0$

INT/STND bit = "1" : Setting of interrupt period INT/STND bit = "0" : Setting of periodic waveform

| t <sub>1</sub> | t <sub>0</sub> | Period      |

|----------------|----------------|-------------|

| 0              | 0              | 1/64 second |

| 0              | 1              | 1 second    |

| 1              | 0              | 1 minute    |

| 1              | 1              | 1 hour      |

The duration that the periodic waveform output is at "L" level is about 7.8ms.  $t_1$  and  $t_0$  determine the output timing of the STD.P output.

e.g.) When

$$t_1$$

="1",  $t_0$ ="1", MASK="0"

When writing into the 30-sec ADJ bit, a carry can occur.

Therfore, if  $(t_1, t_0) = (1, 0)$ , (1, 1), the STD.P output may sometime be at "L" level. When INT/STND="0", this "L" level is kept for a maximum of 9.8ms after under-second digits in 30-sec ADJ is cleared (the 30-sec ADJ flag returns to "0").

If the selected interrupt period is 1 second, 1 minute, or 1 hour, and if a carry occurs during the time the  $S_1$ ,  $S_{10}$ ,  $MI_1$ ,  $MI_{10}$  registers are overwritten using the HOLD bit, and if data written in these registers determines the interrupt timing set by the carry, the STD.P output will go to "L" level after HOLD="0". (IRQ-F will is set to "1")

In other cases, writing to the  $S_1$ ,  $S_{10}$ ,  $MI_1$ ,  $MI_{10}$ ,  $H_1$  registers do not change the STD.P output.

• INT/STND (interrupt-to-Standard waveform switching bit)

INT/STND = "1": "1" of the IRQ-F bit and "L" level on the STD.P output are kept until IRQ-

F (C<sub>D</sub> register) is read out.

INT/STND = "0": "1" of the IRQ-F bit returns to "0" after a certain time elapses (after about a certain time) and the IRQ-F bit returns to "0" after a certain time elapses (after about a certain time). The interest of the IRQ-F bit returns to "0" after a certain time elapses (after about a certain time). The interest of the IRQ-F bit returns to "0" after a certain time elapses (after about a certain time). The interest of the IRQ-F bit returns to "0" after a certain time elapses (after about a certain time). The interest of the IRQ-F bit returns to "0" after a certain time). The interest of the IRQ-F bit returns to "0" after a certain time elapses (after about a certain time). The interest of the IRQ-F bit returns to "0" after a certain time). The interest of the IRQ-F bit returns to "0" after a certain time elapses (after a certain time). The interest of the IRQ-F bit returns to "0" after a certain time). The interest of the IRQ-F bit returns to "0" after a certain time). The interest of the IRQ-F bit returns to "0" after a certain time). The interest of the IRQ-F bit returns to "0" after a certain time elapses (after a certain time). The interest of the IRQ-F bit returns to "0" after a certain time elapses (after a certain time). The interest of the IRQ-F bit returns to "0" after a certain time elapses (after a certain time). The interest of the IRQ-F bit returns the IRQ-F bit

7.8ms) or when IRQ-F is read out.

"L" level on the STD.P output returns to high impedance after a certain time elapses.

#### MASK

"1" of the MASK bit inhibits the setting of "1" to the IRQ-F flag and sets the STD.P output to the high impedance state.

Interrupt mode (INT/STND="1")

Periodic timing waveform output mode (INT/STND="0")

When the IRQ-F bit is read out before auto-return, the IRQ-F bit goes to "0", and the STD.P output keeps "L" level for about 7.8ms, then goes into the high impedance state.

# C<sub>F</sub> REGISTER (Control F Register)

#### TEST

The TEST bit is used for testing by OKI and should be set to "0". This bit can be cleared to "0" by setting the CE pin to "L" level.

#### • 24/12

This bit is used to switch between 24-hour system and 12-hour system.

24/12 = "1" : 24-hour system without PM/AM

24/12 = "0" : 12-hour system with PM/AM

When the 24/12 bit is overwritten, data in the  $H_1 \sim W$  registers may become undefined. Therefore, it is required to newly set those registers again.

#### STOP

"1" of this bit stops clocking and "0" restarts clocking.

#### REST

"1" of this bit clears under-second-time to zero and at the same time stops clocking. "0" of this bit restarts clocking.

Take care not to set the TEST bit to "1" when writing "0" into the REST bit.

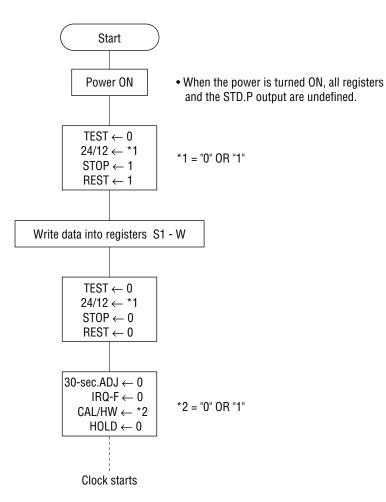

#### **Usage**

## **Functional Description**

Writing and reading are executed in units of 4 bits after the CE input goes high. If the CE input goes low before 4-bit data input is complete, the 4-bit data written when the CE input goes low is ignored. (Data written before the CE input goes low is valid)

Writing and reading are executed starting from the LSB.

#### (WRITE)

- 1) The first 4 bits that are input after the CE input goes high are specified as "3" indicating the WRITE mode. The address to be written is set into the second 4 bits.

- 2) The third 4 bits are written into the previously-set address.

The following 4-bit data are sequentially written into automatically-incremented addresses.

- 3) The address is automatically incremented in a loop way where address F is followed by address 0.

## (READ)

- 1) The first 4 bits that are input after the CE input goes high are specified as "C" indicating the READ mode.

- The address to be read is set into the second 4 bits.

- 2) The third 4-bit data is read from the previously-set address.

The following 4-bit data are sequentially read from automatically incremented addresses.

- 3) The address is automatically incremented in a loop way where address F is followed by address 0.

If a character other than "C" or "3" is specified to the mode setting code, the following data is ignored and the DATA I/O pin keeps the input state.

# **Power Supply**

Reading of registers S<sub>1</sub> ~ W

- Note 1) Data in registers  $C_D$ ,  $C_E$ ,  $C_F$ , or registers S1 to W which are used as RAM can be read out without using fr.

- Note 2) Checking fr is complete by checking only the last digit of fr which has been read out.

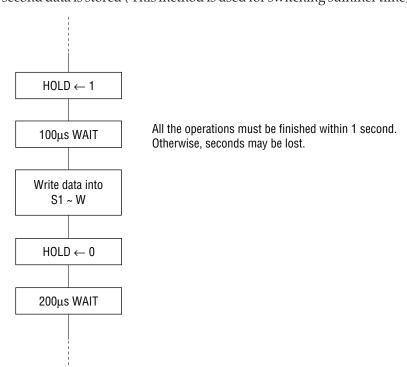

Writing data to S<sub>1</sub> - W

Method 1: When under-second data is not stored

Method 2: When under-second data is stored (This method is used for switching summer time).

# Writing 30-sec ADJ bit

# Method 1

# Method 2

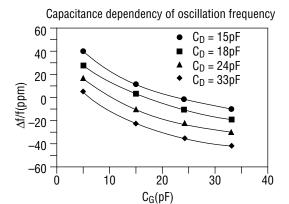

#### REFERENCE DATA

Crystal quartz: Citizen-made CFS-308

$$C_G = 18pF$$

$C_D = 18pF$