# MSM6636 USER'S GUIDE

Oki Electric Industry Co., Ltd.

SUNSTAR电子元器件 http://www.sunstare.com/ TEL: 0755-83778810 FAX:0755-83376182 E-MAIL:szss200163.com

### **INTRODUCTION**

This manual describes the functions of SAE-J1850 protocol and introduces its application examples. This manual also details the functions of MSM6636, and introduces control examples of a LAN (Local Area Network) using MSM6636. For details on the commands of MSM6636, see "MSM6636 Users Manual".

<u>NOTICE</u>

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents cotained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 1995 Oki Electric Industry Co., Ltd.

Printed in Japan

### TABLE OF CONTENTS

| СНАРТ  | ER 1 INTRODUCTION1-1                                       |

|--------|------------------------------------------------------------|

|        |                                                            |

| 1.1    | What is J1850?1-2                                          |

| 1.2    | LAN Configuration of J18501-2                              |

| 1.3    | Bit Format of J18501-3                                     |

| 1.4    | Asynchronous Transmission Communication System of J18501-4 |

| 1.5    | Multiplex Transmission Communication System of J18501-4    |

| 1.6    | Communication Format of J18501-5                           |

|        | 1.6.1 In-frame response type1-7                            |

|        | 1.6.2 Message type                                         |

| OLIADT |                                                            |

| CHAPI  | ER 2 MSM6636 INTERNAL REGISTER LIST2-1                     |

| 2.1    | Description on Internal Registers2-3                       |

|        |                                                            |

| CHAPT  | ER 3 INITIALIZING MSM6636                                  |

| 3.1    | Initializing Node                                          |

| 3.2    | Initializing Network                                       |

| СЦАРТ  | ER 4 MESSAGE TRANSMISSION AND RESPONSE RECEIVE             |

| CHAPI  |                                                            |

|        | OPERATION4-1                                               |

| 4.1    | Message Transmission Operation of IFR Type 04-1            |

| 4.2    | Message Transmission and Response Receive                  |

|        | Operation of IFR Type 1 (addressing by functional address) |

| 4.3    | Message Transmission and Response Receive                  |

|        | Operation of IFR Type 1 (addressing by physical address)   |

| 4.4    | Message Transmission and Response Operation of IFR Type 2  |

| 4.5    | Message Transmission and Response Operation of IFR Type 3  |

|        |                                                            |

| CHAPT | ER 5 MESSAGE RECEIVE AND RESPONSE TRANSMISSION                    |      |

|-------|-------------------------------------------------------------------|------|

|       | OPERATION                                                         | 5-1  |

| 5.1   | Message Receive Operation of IFR Type 0                           | 5-1  |

| 5.2   | Message Receive and Response Transmission Operation of IFR Type 1 |      |

| 5.3   | Message Receive and Response Transmission Operation of IFR Type 2 |      |

| 5.4   | Message Receive and Response Transmission Operation of IFR Type 3 |      |

| СНАРТ | ER 6 CPU INTERRUPT                                                | 6-1  |

| 6.1   | Receive Message Length Error Interrupt (LEN)                      | 6-3  |

| 6.2   | LAN Bus Dominant Time Length Error Interrupt (ABN)                | 6-6  |

| 6.3   | Local Bus Driver Error Interrupt (D-P)                            | 6-6  |

| 6.4   | Overrun Error Interrupt (OVER)                                    | 6-7  |

| 6.5   | CRC Error Interrupt (CRC)                                         | 6-8  |

| 6.6   | Message Format Error Interrupt (FORM)                             | 6-9  |

| 6.7   | Bit Format Error Interrupt (INV)                                  | 6-10 |

| 6.8   | IFS Error Interrupt (IFS)                                         | 6-11 |

| 6.9   | Bus Busy Interrupt (BUSY)                                         | 6-12 |

| 6.10  | Non ACK Interrupt (NOACK)                                         | 6-14 |

| 6.11  | Response Transmission Standby Error Interrupt (NRSP)              | 6-15 |

| 6.12  | Break Receive Interrupt (BRK)                                     | 6-16 |

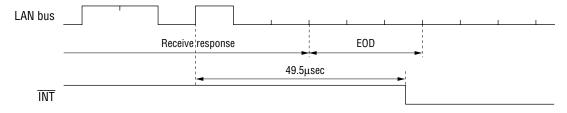

| 6.13  | Response Receive Completion Interrupt (RSP)                       | 6-16 |

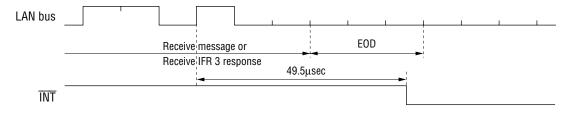

| 6.14  | Message Receive Completion Interrupt (RCV)                        | 6-17 |

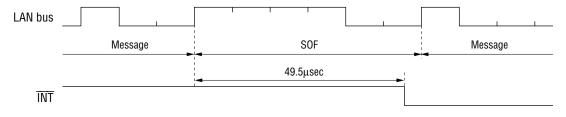

| 6.15  | Message Transmission Completion Interrupt (TR)                    | 6-18 |

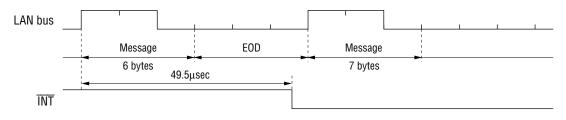

| 6.16  | Parity Error Interrupt (PAR)                                      | 6-18 |

| 6.17  | Wake Up Interrupt by RXD (WAKR)                                   | 6-19 |

| 6.18  | Wake Up Interrupt by LAN Bus (WAKD)                               | 6-19 |

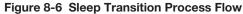

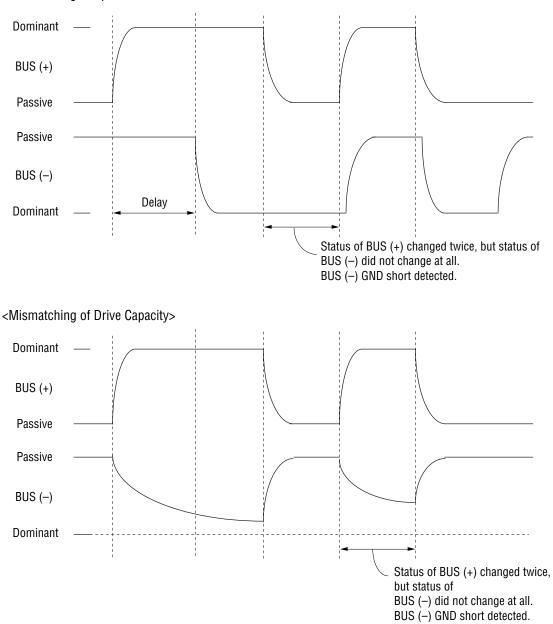

| 6.19  | LAN Bus (-) GND Short Detection Interrupt (BNG)                   | 6-20 |

| 6.20  | LAN Bus (+) V <sub>DD</sub> Short Detection Interrupt (BPV)       | 6-20 |

| 6.21  | LAN Bus (-) V <sub>DD</sub> Short Detection Interrupt (BNV)       | 6-21 |

| 6.22  | LAN Bus (+) GND Short Detection Interrupt (BPG)                   | 6-21 |

###

| CHAPTER 8 SLE                                                                                                                     |                                                                                                                            | 8-1                       |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------|

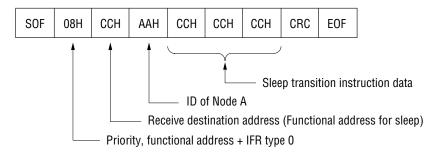

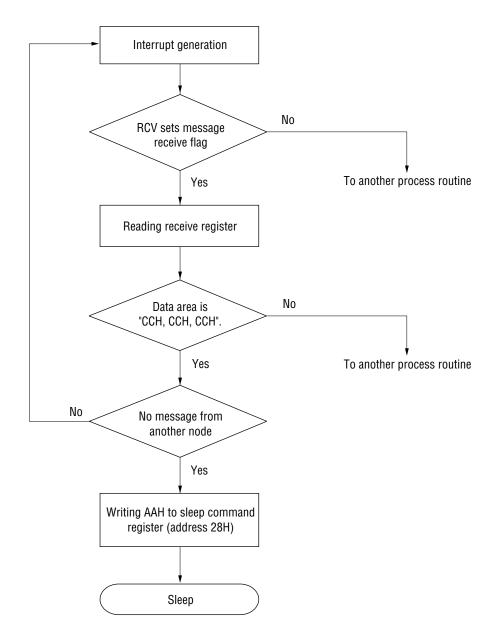

| 8.1 Example of                                                                                                                    | of Sleep Conversion Routine                                                                                                | 8-3                       |

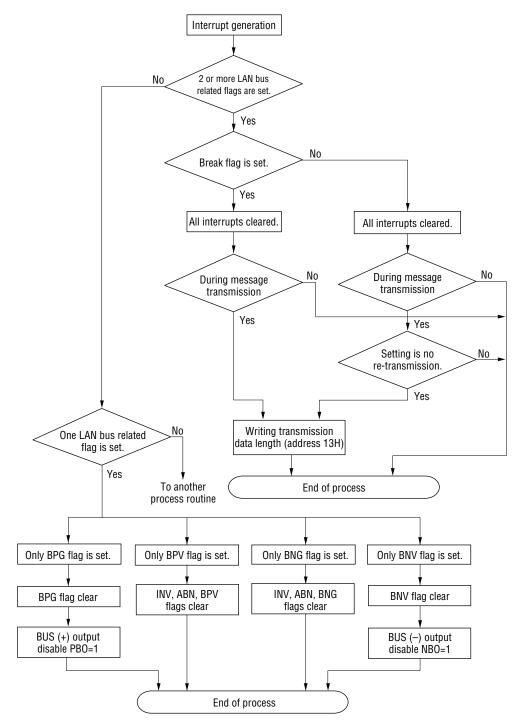

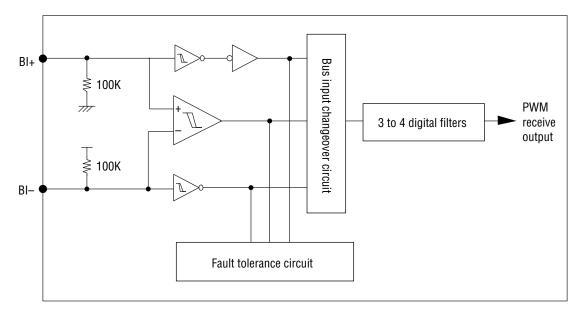

| CHAPTER 9 FAU                                                                                                                     | JLT TORERANT FUNCTION                                                                                                      | 9-1                       |

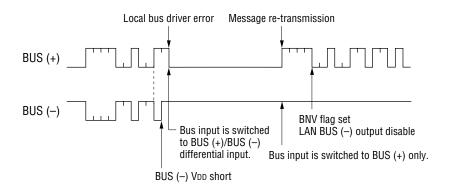

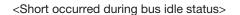

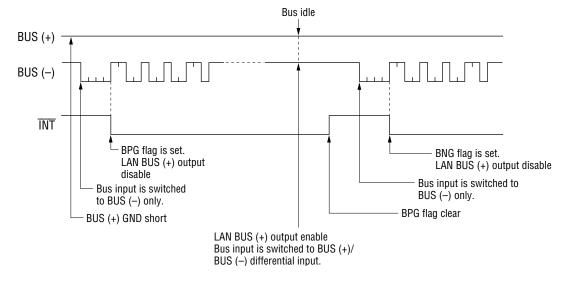

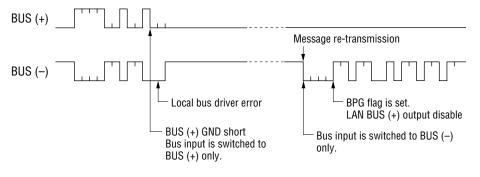

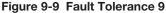

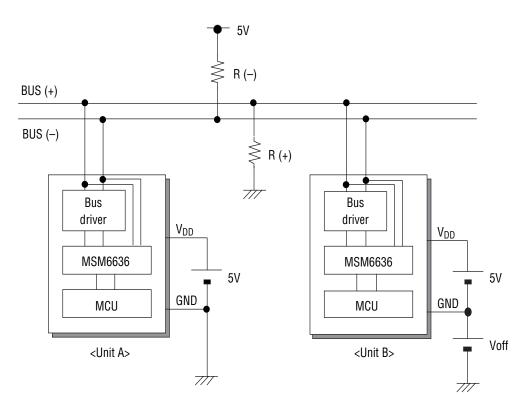

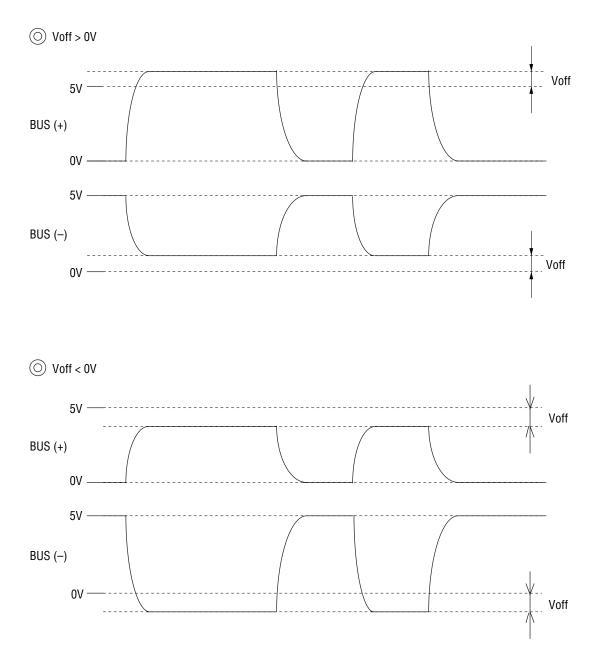

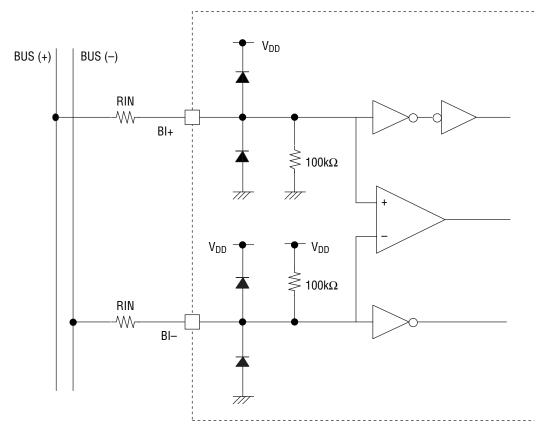

| <ul> <li>9.2 Bus (-) V<sub>D</sub></li> <li>9.3 Bus (+) GI</li> <li>9.4 Bus (+) V<sub>D</sub></li> <li>9.5 LAN Bus (+)</li> </ul> | ND Short<br>DD Short<br>ND Short<br>DD Short<br>Open<br>s of Fault Tolerant Function Process Routine                       | 9-3<br>9-6<br>9-8<br>9-10 |

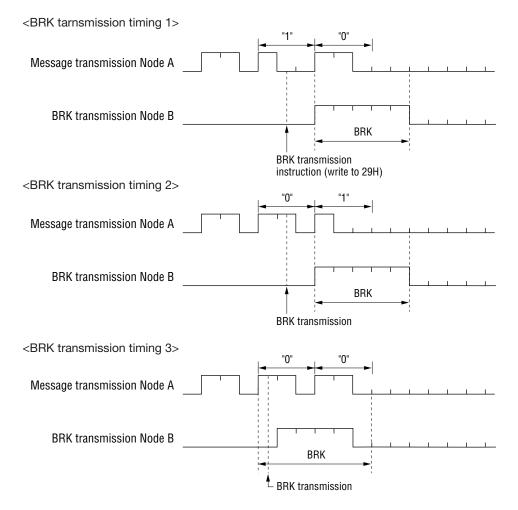

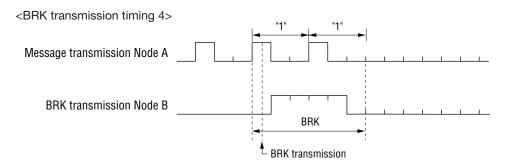

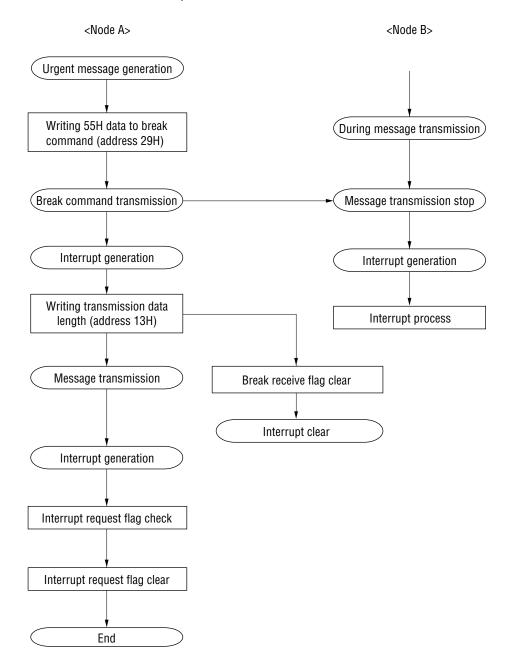

| CHAPTER 10 BR                                                                                                                     | REAK FUNCTION                                                                                                              | 10-1                      |

| 10.1 Examples                                                                                                                     | of Break Function Routine                                                                                                  | 10-3                      |

| CHAPTER 11 CC                                                                                                                     | OMMUNICATION EXAMPLE USING IFR TYPE 3                                                                                      | 11-1                      |

| 11.1 How to Us                                                                                                                    | se NAK Register                                                                                                            | 11-3                      |

| CHAPTER 12 BU                                                                                                                     | JS DRIVER                                                                                                                  | 12-1                      |

| CHAPTER 13 SO                                                                                                                     | OURCE OSCILLATION FREQUENCY TOLERANCE                                                                                      | 13-1                      |

|                                                                                                                                   | scillation Frequency Tolerance of Arbitration Functionscillation Frequency Tolerance of Communication Function             |                           |

| CHAPTER 14 PR                                                                                                                     | RECAUTIONS WHEN DESIGNING LAN USING MSM6636                                                                                | 14-1                      |

| 14.2 Precautio<br>14.3 GND Offs<br>14.4 CPU Inter                                                                                 | ns for LAN Bus Design<br>ns for Bus Driver Design<br>set<br>rface Selection and Message Receive Processing Time<br>Process | 14-5<br>14-7<br>14-10     |

# INTRODUCTION

SUNSTAR电子元器件 http://www.sunstare.com/ TEL: 0755-83778810 FAX:0755-83376182 E-MAIL:szss200163.com

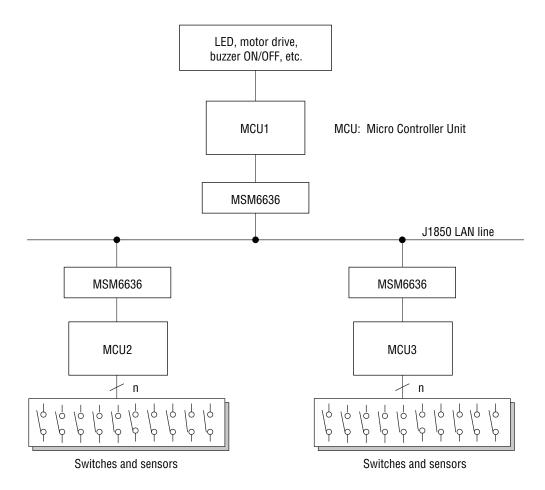

### 1. INTRODUCTION

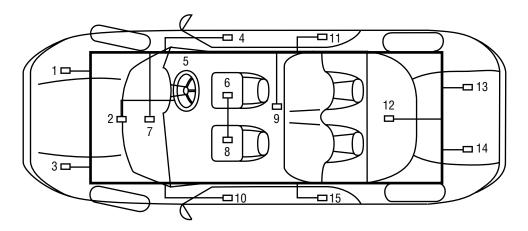

Many wiring connectors are used for various switches, sensors, lights and motors positioned throughout automobiles. To interconnect these devices efficiently using multiplex transmission communication technology, a small scale LAN (Local Area Network) is constructed, and data communication between devices is performed using common lines. SAE-J1850 is a communication format (protocol) of multiplex transmission communication adapted by the Society of Automotive Engineers (SAE) in the United States. MSM6636 is an automotive LAN controller based on this protocol. MSM6636 can be applied not only to the control of various devices in automobiles, as shown below, but also to integrated vehicle control systems, such as car navigation, car audio and electronic control 4WD, and to on-vehicle problem diagnosis systems.

- 1. Front right area control

- 2. Front window control

- 3. Front left area control

- 4. Front right door control

- 5. Switch module control

- 6. Driver seat control

- 7. Total warning control

- 8. Seat next to driver control

- 8. Seat next to driver control

- 9. Roof control

- 10. Front left door control

- 11. Rear right door control

- 12. Rear window control

- 13. Rear right area control

- 14. Rear left area control

- 15. Rear left door control

### Figure 1-1 Automotive LAN

### 1.1 What is J1850?

An overview of the communication regulation of J1850 protocol is shown below. In J1850, each node (communication station) connected to the LAN can transmit messages equally, and has an address (physical address and functional address) to identify itself. A physical address is an address unique to each node. There is no other node with the same physical address on the LAN. A functional address, on the other hand, is an address to send messages at the same time to devices which have the same function. This means that multiple nodes which have the same function have the same functional address.

Communication is performed by specifying the receive destination address in the message. If the physical address is specified to the receive destination address, only the specified node will receive the message. If the functional address is specified to the receive destination address, multiple nodes will receive the message.

There is a function for the node which received the message to return its physical address value (response transmission) when it receives the message normally. By this function, the message transmission node can know whether the specified receive destination node received the message normally.

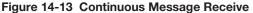

### 1.2 LAN Configuration of J1850

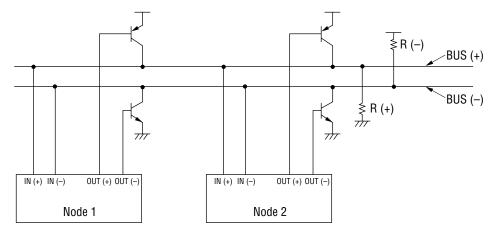

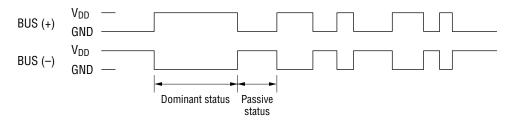

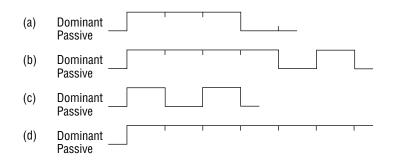

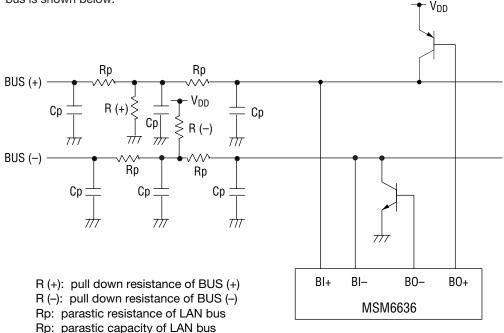

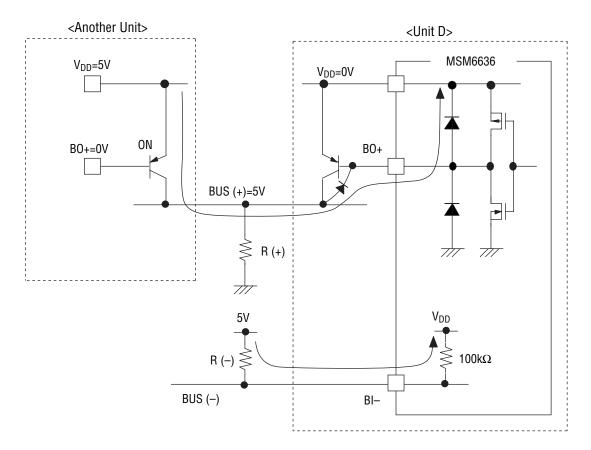

Figure 1-2 shows the LAN configuration of J1850. The LAN bus uses 2 lines: BUS (+) and BUS (-). BUS (+) is connected to ground (GND) with resistance R (+), and BUS (-) is connected to power supply (VDD) with resistance R (-). At each node, the PNP transistor bus driver is connected to BUS (+), and the NPN transistor bus driver is connected to BUS (-), to drive the LAN bus. Inverted signals (Figure 1-3) are output to both BUS (+) and BUS (-). When node 1 turns the bus drivers on (turns the PNP and NPN transistors on), BUS (+) becomes VDD potential and BUS (-) becomes GND potential. Even if node 2 turns the bus drivers on or off after this, the status of BUS (+) and BUS (-) does not change. This status is called "node 1 is occupying the bus", and the status of BUS (+) and BUS (+) and BUS (-) at this time is called "dominant status". Only when all nodes connected to the LAN turn the bus drivers off, BUS (+) becomes GND potential, and BUS (-) becomes VDD potential. This status is called "the bus is open", and the status of BUS (+) and BUS (-) becomes VDD potential. This status is called "the bus is open", and the status of BUS (+) and BUS (-) at this time is called "passive status". The format in which transistors of multiple nodes are connected to one common line in this manner is called a "wired OR" connection.

Figure 1-2 Configuration fo J1850 LAN

Figure 1-3 Signal Wave Form of BUS (+) and BUS (-)

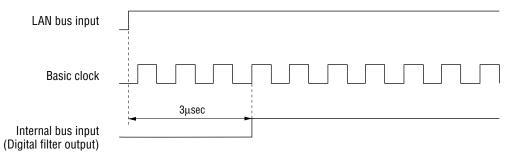

1.3 Bit Format of J1850

In J1850, a message signal output to the LAN bus is detected by the status whether the bus is or is not occupied for a specified "short time". In other words, communication is performed by pulse width modulation (PWM).

In J1850, codes (bits) necessary for several types of communication are expressed by a combination of bus occupancy and bus open as follows.

| Code | Contents                                                                                                | Combination of Bus<br>Occupancy/Open                                                                 | Wave Form |

|------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------|

| SOF  | Indicates beginning of message frame<br>(Start Of Frame)                                                | Bus is continuously occupied for 4<br>short time units, then bus is opened for<br>2 short time units |           |

| "1"  | Indicates binary bit "1".                                                                               | Bus is occupied for 1 short time unit,<br>then bus is opened for 2 short time<br>units.              |           |

| "0"  | Indicates binary bit "0".                                                                               | Bus is continuously occupied for 2 short time units, then bus is opened for one short time units.    |           |

| EOD  | Indicates end of transmission data<br>(END Of Data)                                                     | Bus is continuously opened for 3 short time units.                                                   | <u></u>   |

| EOF  | Indicates end of message frame<br>(End Of Frame)                                                        | Bus is continuously opened for 6 short time units.                                                   | <u></u>   |

| IFS  | Indicates interval period to distinguish<br>one message frame from another.<br>(Inter-Frame Separation) | Bus is continuously opened for 3 short time units.                                                   | <u></u>   |

| BRK  | Indicates a force-stop of<br>communication.<br>(Break)                                                  | Bus is continuously occupied for 5<br>short time units, then bus is opened for<br>1 short time unit. |           |

### Figure 1-4 PWM Bit Format of J1850

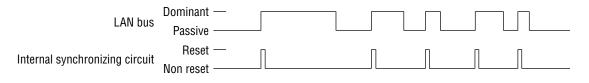

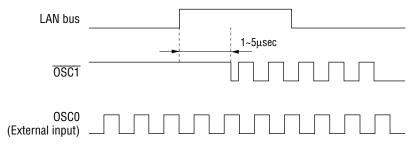

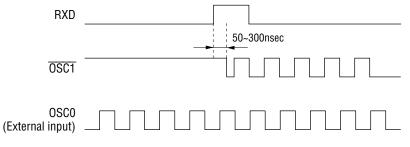

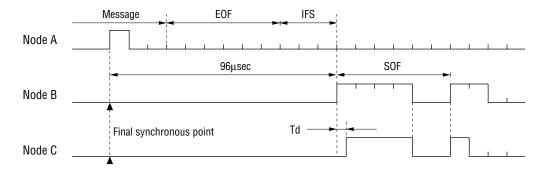

### 1.4 Asynchronous Transmission Communication System of J1850

In J1850, communication is performed asynchronously. This communication is implemented by making the communication speed of all nodes of the LAN equal. This means that by communicating using certain small time units of the PWM bit format, a node on the LAN receives a message synchronizing the internal circuit when the occupancy of the bus starts (when the bus changes from passive to dominant status). When transmitting a message, the message is sent according to the timing of the node sending message, with the receive node synchronizing the transmission node. Since each bit of the PWM system synchronizes, there is little deviation of the data sample for start-stop synchronization. This makes high-speed communication possible.

Figure 1-5 Synchronization of J1850

### 1.5 Multiplex Transmission Communication System of J1850

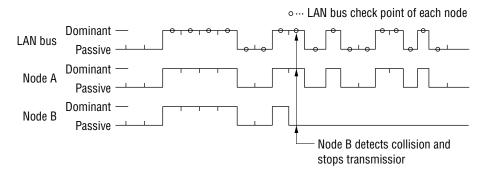

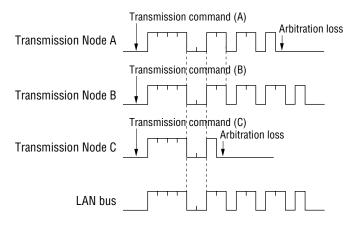

For all nodes on the LAN to start communication (message communication) according to the respective request, it is necessary to avoid collision which occurs when transmission starts at the same time. There are various means to prevent collision, and in the J1850, CSMA/CD (Carrier Sense Multiple Access/Collision Detection) is used. In this system, collision is avoided by "stopping transmission and re-transmission". Each node checks the bus status at every small time unit, and starts transmission after confirming that the bus is in idle status (status in which the passive status of the bus is continuing for a certain time). The bus is continuously checked during transmission, judging whether the data transmitted by the local node is output normally to the bus. If a message transmission node is outputting a passive status to the bus while the bus is in dominant status, the node detects collision, and stops transmission. This in no way affects the message of the node outputting dominant status to the bus, so this node continues message transmission. By avoiding collision in this way, all nodes on the LAN can perform message transmission at any time equally. Using this system, priorities can be assigned to messages, which improves network efficiency.

### 1.6 Communication Format of J1850

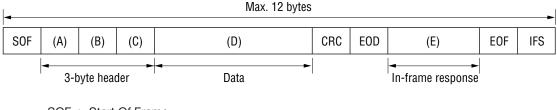

The frame format of J1850 follows.

SOF : Start Of Frame

CRC: Cyclic Redundancy Check

EOD: End Of Data

EOF : End Of Frame

IFS : Inter-Frame Separation

| $\geq$ | No. of Bytes | Content                                                |

|--------|--------------|--------------------------------------------------------|

| (A)    | 1            | Priority and message type                              |

| (B)    | 1            | Physical address or functional address of receive node |

| (C)    | 1            | Physical address of transmission node                  |

| (D)    | *1           | Data                                                   |

| CRC    | 1            | CRC code                                               |

| (E)    | *1           | In-frame response (IFR)                                |

#### Table 1-1 Communication Format

\*1 Sum of number of bytes of (D) and number of bytes of (E) is 0~8 bytes.

(A) Bit configuration of priority and message type

| 7      | 6  | 5  | 4  | 3 | 2 | 1  | 0  |

|--------|----|----|----|---|---|----|----|

| H (P3) | P2 | P1 | P0 | К | Y | Z1 | Z0 |

H .....Header format setting bit 0: 3 byte header 1:1 byte header (MSM6636 does not support 1 byte headers.)

P2, P1, P0 .... Priority setting bit When multiple nodes on a network start message transmission at the same time, these bits determine the priority of the messages. The smaller the priority value, the higher the priority. MSM6636 can use the "H bit" as the priority setting bit.

(Supplement)

MSM6636 is designed based on the J1850 standard issued in December 1991. Under the current standard, however, the position of the H bit and P2~P0 bits are different, due to partial standard changes by SAE. This does not cause hardware problems in the MSM6636, since the H bit is not used to control 3 byte/1 byte header selection (fixed to a 3-byte header). If meeting the latest standard is considered, design software which handles P3~P1 bits as a priority field.

Y .....Address type setting bit

0: Specifies the functional address to address (B) of the receive node.

1: Specifies the physical address to address (B) of the receive node.

K, Z1, Z0 ..... In-frame response type setting bit

The response type is set by a combination of K, Z1 and Z0 bits.

The message type and response type are determined by the low-order 4 bits of the header byte (A), including the Y bit. The classification is shown below.

|   | ZZ<br>KY10 | Address<br>Type | IFR Type | Message Type                                  |

|---|------------|-----------------|----------|-----------------------------------------------|

| 0 | 0000       | Functional      | 2        | Receives multiple IDs from multiple listeners |

| 1 | 0001       | 1               | 1        | Broadcast (*1)                                |

| 2 | 0010       | 1               | 2        | Receives multiple IDs from multiple listeners |

| 3 | 0011       | 1               | 3        | Receives DATA from selected listeners         |

| 4 | 0100       | Physical        | 1        | Receives ID from selected listener            |

| 5 | 0101       | 1               | 3        | Receives DATA from selected listener          |

| 6 | 0110       | 1               | 0        | SEA reserve (*2)                              |

| 7 | 0111       | 1               | 3        | Receives DATA from selected listener          |

| 8 | 1000       | Functional      | 0        | To multiple listeners (command/status)        |

| 9 | 1001       | 1               | 1        | To multiple listeners (request)               |

| A | 1010       | 1               | 1        | _                                             |

| В | 1011       | 1               | 1        |                                               |

| C | 1100       | Physical        | 1        |                                               |

| D | 1101       | 1               | 1        |                                               |

| E | 1110       | 1               | ↑        |                                               |

| F | 1111       | 1               | ↑        |                                               |

Table 1-2 Message Type and IRF Type List

(\*1) Broadcast : Sends the same data to multiple listeners selected by the functional address. Only the listener with the highest priority ID (physical address) can send the ID as an IFR. (IFR can be sent only once. Other listeners cannot send an IFR.)

(\*2) SAE reserve : MSM6636 does not respond, even if an IFR request is received by this header.

For details on IFR types, see "1.6.1 In-frame response type".

(B) Physical address or functional address of receive node

The 1st byte (A) of the 3 byte header (Y bit) selects whether an address is physical or functional, and the 2nd byte (B) indicates the address of the receive node.

(C) Physical address of transmission node

Indicates the physical address (ID) of the transmission node.

(D) Data

> Indicates arbitrary transmission data. Data is increased or decreased in byte units. The maximum number of bytes is 8, including the response.

In-frame response (E)

> The message transmission node can request a response within the message frame to the message receive node. This response is called an "in-frame response".

#### 1.6.1 In-frame response type

An in-frame response is transmitted or received within 1 message frame to make communication efficient. The four types follow.

<IFR type 0>

Does not request an in-frame response.

| SOF | HEADER | DATA | CRC | EOF |

|-----|--------|------|-----|-----|

|-----|--------|------|-----|-----|

<IFR type 1>

Requests an ID (physical address) from one receive node as an in-frame response.

| SOF | HEADER | DATA | CRC | EOD | ID | EOF |

|-----|--------|------|-----|-----|----|-----|

|-----|--------|------|-----|-----|----|-----|

<IFR type 2>

Requests an ID from multiple receive nodes as an in-frame response. In this type, an ID is sent from the receive nodes in sequence according to their ID priority.

| SOF | HEADER | DATA | CRC | EOD | ID1 |  | IDn | EOF |

|-----|--------|------|-----|-----|-----|--|-----|-----|

|-----|--------|------|-----|-----|-----|--|-----|-----|

<IFR type 3>

Request multi-byte data with CRC from one receive node as an in-frame response.

| SOF | HEADER | DATA | CRC | EOD | IFR DATA | CRC | EOF |

|-----|--------|------|-----|-----|----------|-----|-----|

|-----|--------|------|-----|-----|----------|-----|-----|

### 1.6.2 Message type

Message types are classified by a combination of address type setting bit Y and the in-frame response type setting bits K, Z1 and Z0.

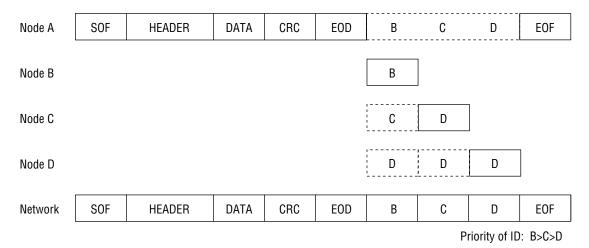

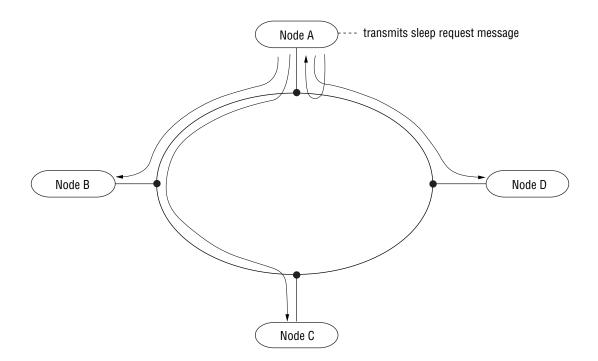

(a) Functional address +IFR type 2

Since the functional address is specified as the address of the receive node, multiple nodes can receive a message. The physical address (ID) is requested from all of the receive nodes as a response. Node A=message transmission node, Nodes B, C and D=message receive nodes and message status on the network are shown below.

When each message receive node enters the in-frame response transmission area, each message receive node starts to send an ID. The sequence of sending a response starts from the receive node with the higher priority ID. A node with a low priority ID waits for completion of the response transmission of the nodes with higher priority IDs, and then starts sending a response. Nodes which have completed a response transmission do not send a response again. Such a response transmission process is repeated for the number of receive nodes.

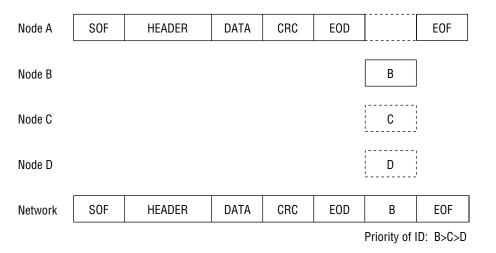

### (b) Functional address + IFR type 1

An ID is sent from multiple nodes as a response, just as in "(a)", but a response is sent only from the receive node with the highest priority ID, and response transmission is completed. A response is sent only once. The other receive nodes cannot send a response.

### (c) Functional address + IFR type 3

Multiple byte data with CRC is sent from multiple nodes as a response. In this case as well, just as in "(b)", only the receive node with the highest priority sends a multiple byte data response, and the response transmission is completed. A response is sent only once. The other receive nodes cannot send a response.

|         |     |        |      |     |     | <b>.</b>         |     |     |

|---------|-----|--------|------|-----|-----|------------------|-----|-----|

| Node A  | SOF | HEADER | DATA | CRC | EOD |                  |     | EOF |

|         |     |        |      |     |     | [                |     |     |

| Node B  |     |        |      |     |     | IFR DATA         | CRC |     |

|         |     |        |      |     |     |                  |     |     |

| Node C  |     |        |      |     |     | ,<br>,<br>,<br>, |     |     |

|         |     |        |      |     |     |                  |     |     |

| Node D  |     |        |      |     |     | <br> <br> <br>   |     |     |

|         |     |        |      |     |     | 1                |     |     |

| Network | SOF | HEADER | DATA | CRC | EOD | IFR DATA         | CRC | EOF |

|         |     |        |      |     |     | Duisuites        |     |     |

Priority of IFR DATA: B>C>D

### (d) Physical address +IFR type 1

Since a physical address is specified as the address of the receive node, one node receives the message. In this case, communication is one to one, and the message receive node sends an ID as the response.

| Node A  | SOF             | HEADER                                                                                | DATA                    | CRC                     | EOD                      | В                       | EOF        |             |            |

|---------|-----------------|---------------------------------------------------------------------------------------|-------------------------|-------------------------|--------------------------|-------------------------|------------|-------------|------------|

| Node B  |                 |                                                                                       |                         |                         |                          | В                       |            |             |            |

| Network | SOF             | HEADER                                                                                | DATA                    | CRC                     | EOD                      | В                       | EOF        | ]           |            |

| (e)     | Physic          | cal address +IFR                                                                      | type 3                  |                         |                          |                         |            |             |            |

|         |                 | nunication is one<br>lata with CRC as                                                 |                         |                         | d)", and t               | he messa                | ge receive | e node ser  | nds multi- |

| Node A  | SOF             | HEADER                                                                                | DATA                    | CRC                     | EOD                      |                         |            |             | EOF        |

| Node B  |                 |                                                                                       |                         |                         |                          | IFR D                   | )ATA       | CRC         |            |

| Network | SOF             | HEADER                                                                                | DATA                    | CRC                     | EOD                      | IFR D                   | ATA        | CRC         | EOF        |

| (f)     | Since<br>transr | cal address or fu<br>a response is n<br>nission ends. In<br>tion without jud<br>ally. | ot request<br>this case | ted, the m<br>, message | nessage fi<br>e transmis | rame is co<br>sion node | complete   | es the trar | nsmission  |

| Node A  | SOF             | HEADER                                                                                | DATA                    | CRC                     | EOF                      |                         |            |             |            |

| Node B  |                 |                                                                                       |                         |                         |                          |                         |            |             |            |

| Network | SOF | HEADER | DATA | CRC | EOF |

|---------|-----|--------|------|-----|-----|

|---------|-----|--------|------|-----|-----|

## MSM6636 INTERNAL REGISTER LIST

### 2. MSM6636 INTERNAL REGISTER LIST

The MSM6636 internal register list is shown below. For details on each register, see "2.1 Description on internal registers".

| Address | MSB | _   | _   | _   | _   | _   | _   | LSB | Register Content               | Register Name   | R/W |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|--------------------------------|-----------------|-----|

| 00      | Н   | P2  | P1  | P0  | K   | Y   | Z1  | Z0  | Communication type             |                 |     |

| 01      | RA7 | RA6 | RA5 | RA4 | RA3 | RA2 | RA1 | RA0 | Receive destination address    |                 |     |

| 02      | _   | —   |     | —   | —   | _   | —   | —   | —                              |                 |     |

| 03      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | DO  | Transmission data              |                 |     |

| 04      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | DO  | Transmission data              | Transmission    |     |

| 05      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | DO  | Transmission data              | register        |     |

| 06      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | DO  | Transmission data              |                 |     |

| 07      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Transmission data              |                 |     |

| 08      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Transmission data              |                 |     |

| 09      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Transmission data              |                 |     |

| 0A      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Transmission data              |                 |     |

| 0B      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | IFT data                       |                 | W   |

| 0C      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | DO  | IFT data                       |                 |     |

| 0D      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | IFT data                       |                 |     |

| 0E      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | IFT data                       | Response        |     |

| 0F      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | IFT data                       | register        |     |

| 10      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | IFT data                       |                 |     |

| 11      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | IFT data                       |                 |     |

| 12      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | IFT data                       |                 |     |

| 13      | —   | _   | _   | _   | DL3 | DL2 | DL1 | DLO | Transmission<br>data length    | Transmission    |     |

| 14      | —   | —   | _   |     | RL3 | RL2 | RL1 | RL0 | Response data length           | status register |     |

| 15      | Н   | P2  | P1  | P0  | K   | Y   | Z1  | Z0  | Communication type             |                 |     |

| 16      | RA7 | RA6 | RA5 | RA4 | RA3 | RA2 | RA1 | RA0 | Receive destination address    |                 |     |

| 17      | TA7 | TA6 | TA5 | TA4 | TA3 | TA2 | TA1 | TA0 | Transmission<br>source address |                 |     |

| 18      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | DO  | Receive data                   |                 |     |

| 19      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | DO  | Receive data                   | Receive         |     |

| 1A      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | DO  | Receive data                   | register        | R   |

| 1B      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | DO  | Receive data                   |                 |     |

| 1C      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | DO  | Receive data                   |                 |     |

| 1D      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | DO  | Receive data                   |                 |     |

| 1E      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Receive data                   |                 |     |

| 1F      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Receive data                   |                 |     |

### Table 2-1 Internal Register List (1/2)

**2-1** SUNSTAR电子元器件 http://www.sunstare.com/ TEL: 0755-83778810 FAX:0755-83376182 E-MAIL:szss20@163.com

| Address | MSB  | —     | —    | —    | —   | —    | —   | LSB | Register Content                      | Register Name                         | R/W |

|---------|------|-------|------|------|-----|------|-----|-----|---------------------------------------|---------------------------------------|-----|

| 20      |      | _     | _    | —    | RL3 | RL2  | RL1 | RL0 | Receive data length                   | Receive data<br>length register       | R   |

| 21      |      | _     |      | —    | _   | _    | —   | —   | Completion command                    | Initialization/RD completion register | W   |

| 22      | LEN  | ABN   | D–P  | OVER | CRC | FORM | INV | IFS | Message<br>abnormality flag           | late                                  |     |

| 23      | BUSY | NOACK | NRSP |      | BRK | RSP  | RCV | TR  | Message transmission<br>/receive flag | Interrupt<br>request flag             |     |

| 24      | PAR  | _     | WAKR | WAKD | BPG | BPV  | BNG | BNV | LAN bus flag                          |                                       | DAM |

| 25      | LEN  | ABN   | D–P  | OVER | CRC | FORM | INV | IFS | Message<br>abnormality flag           |                                       | R/W |

| 26      | BUSY | NOACK | NRSP | _    | BRK | RSP  | RCV | TR  | Message transmission<br>/receive flag | Interrupt<br>enable flag              |     |

| 27      | PAR  | _     | WAKR | WAKD | BPG | BPV  | BNG | BNV | LAN bus flag                          |                                       |     |

| 28      | S7   | S6    | S5   | S4   | S3  | S2   | S1  | S0  | Sleep command                         | Sleep command<br>register             | w   |

| 29      | B7   | B6    | B5   | B4   | B3  | B2   | B1  | BO  | BRK transmission command              | Break command<br>register             | W   |

| 2A      | D2   | D1    | DO   | PBO  | NBO | NAK  | N1  | NO  | Mode setting                          | Mode setting register                 |     |

| 2B      | PA7  | PA6   | PA5  | PA4  | PA3 | PA2  | PA1 | PA0 | Physical address                      | Physical address<br>register          |     |

| 2C      | FA7  | FA6   | FA5  | FA4  | FA3 | FA2  | FA1 | FA0 | Functional address                    |                                       |     |

| 2D      | FA7  | FA6   | FA5  | FA4  | FA3 | FA2  | FA1 | FA0 | Functional address                    |                                       |     |

| 2E      | FA7  | FA6   | FA5  | FA4  | FA3 | FA2  | FA1 | FA0 | Functional address                    |                                       |     |

| 2F      | FA7  | FA6   | FA5  | FA4  | FA3 | FA2  | FA1 | FA0 | Functional address                    |                                       |     |

| 30      | FA7  | FA6   | FA5  | FA4  | FA3 | FA2  | FA1 | FA0 | Functional address                    |                                       |     |

| 31      | FA7  | FA6   | FA5  | FA4  | FA3 | FA2  | FA1 | FA0 | Functional address                    |                                       |     |

| 32      | FA7  | FA6   | FA5  | FA4  | FA3 | FA2  | FA1 | FA0 | Functional address                    | Functional                            | R/W |

| 33      | FA7  | FA6   | FA5  | FA4  | FA3 | FA2  | FA1 | FA0 | Functional address                    | address<br>register                   |     |

| 34      | FA7  | FA6   | FA5  | FA4  | FA3 | FA2  | FA1 | FA0 | Functional address                    | regiotor                              |     |

| 35      | FA7  | FA6   | FA5  | FA4  | FA3 | FA2  | FA1 | FA0 | Functional address                    |                                       |     |

| 36      | FA7  | FA6   | FA5  | FA4  | FA3 | FA2  | FA1 | FA0 | Functional address                    |                                       |     |

| 37      | FA7  | FA6   | FA5  | FA4  | FA3 | FA2  | FA1 | FA0 | Functional address                    |                                       |     |

| 38      | FA7  | FA6   | FA5  | FA4  | FA3 | FA2  | FA1 | FA0 | Functional address                    |                                       |     |

| 39      | FA7  | FA6   | FA5  | FA4  | FA3 | FA2  | FA1 | FA0 | Functional address                    |                                       |     |

| 3A      | FA7  | FA6   | FA5  | FA4  | FA3 | FA2  | FA1 | FA0 | Functional address                    |                                       |     |

| 3B      | NA7  | NA6   | NA5  | NA4  | NA3 | NA2  | NA1 | NA0 | NAK return date                       | NAK register                          |     |

### Table 2-1 Internal Register List (2/2)

### 2.1 Description of Internal Registers

Data read and write enable/disable and the status at reset of MSM internal registers are listed below.

| Internal Address | R/W | Register Name                         | Status at Reset |

|------------------|-----|---------------------------------------|-----------------|

| 00H~0AH          | W   | Transmission register                 | Undefined       |

| 0BH~12H          | W   | Response register                     | Undefined       |

| 13H~14H          | W   | Transmission status register          | 00H             |

| 15H~1FH          | R   | Receive register                      | Undefined       |

| 20H              | R   | Receive data length register          | 00H             |

| 21H              | W   | Initialization/RD completion register | —               |

| 22H~24H          | R/W | Interrupt request flag                | 00H             |

| 25H~27H          | R/W | Interrupt enable flag                 | 00H             |

| 28H              | W   | Sleep command register                | 00H             |

| 29H              | W   | Break command register                | 00H             |

| 2AH              | R/W | Mode setting register                 | Undefined       |

| 2BH              | R/W | Physical address register             | Undefined       |

| 2CH~3AH          | R/W | Functional address register           | Undefined       |

| 3BH              | R/W | NAK register                          | Undefined       |

| Table 2-2 | Description | on Internal | Registers |

|-----------|-------------|-------------|-----------|

|-----------|-------------|-------------|-----------|

#### A) Transmission register

A register to write a message for transmission. The content of this register is sent as a message. Write the priority of the message, message type, receive destination address and arbitrary transmission data. The register does not exist at address 02H, but the physical address value at address 2.

BH is automatically sent as the transmission source address when a message is sent. Since CRC code is automatically added at the end of the message, it is not necessary to write CRC code to this register.

This register is write only, and cannot be read data. If this register is read, all 00H is read. Since the register does not exist at address 02H, any data can be written to 02H.

B) Response register

A register to write multi-byte data to be sent as an in-frame response when an IFR type 3 message is received. When sending a response, the number of bytes specified by address 14H is sent sequentially from address 0BH. Since a CRC code is automatically added at the end of the transmission response, it is not necessary to write CRC code to this register.

#### C) Transmission status register

Address 13H is a register to specify the transmission data length. Write the total number of bytes (excluding CRC) of the 3 byte header and the arbitrary transmission data. Message transmission starts by writing this register. A minimum of 3 bytes and a maximum of 12 bytes can be specified as the transmission data length. The maximum number of bytes, however, is different, depending on the type of message to be sent. Write the number of bytes such that the total number of bytes of the message to send and respond (including CRC) do not exceed 12 bytes. If the total number of bytes exceed 12 bytes, a message length error occurs (see "6.1 Receive message length error interrupt"), and normal communication cannot be performed.

Address 14H is a register to specify the IFR type 3 response data length. A minimum of 1 byte and maximum of 7 bytes can be specified as the response data length. Writing this register becomes the IFR type 3 response transmission standby command. This standby status is held until the IFR type 3 message is received, and a response is sent. This status can be reset by a reset input.

D) Receive register

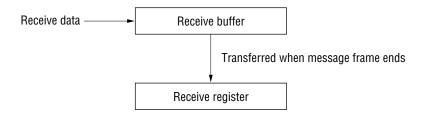

A received message or response is stored sequentially from address 15H. If a message is received, only the received message (including CRC) is stored, the response is not stored. If a message to a request response is sent, only the received response (including the CRC of the response, in the case of an IFR type 3 response) is stored. A received message or response is stored to the receive register when a message frame ends. Since it is stored temporarily to another receive buffer when receiving a message or response, previous received data of the receive register can be read, even when receiving data. The content of the receive buffer, however, cannot be read. When a receive error occurs, data is not transferred from the receive buffer to the receive register, therefore received message data cannot be read at this time.

Figure 2-1 Receive Register

Newly received data is overwritten to the receive register. Since the receive register is not cleared, if the newly received data length is shorter than the previously received data length, the previously received data remains after the newly received data.

E) Receive data length register

The byte length (excluding CRC) of the receive data stored to the receive register is stored. When interrupt request flag RSP or RCV is set, the new receive data length is stored. After reading this register, read the receive register if necessary.

F) Initialization/RD completion register

After initializing or reading the receive register, receiving a new message or response is enabled by writing to this register. There is no specification on data to be written. If the new message or response receiving ends before writing to this register, an overrun error occurs (see "6.4 Overrun error interrupt"), and received data is not stored to the receive register. After inputting a reset, or when interrupt request flag RSP or RCV is set, be certain to write to this register.

G) Interrupt request flag

MSM6636 sets this flag and requests an interrupt to the CPU. There are message related flags, a LAN bus line related flag, etc. in an interrupt request flag. For details, see "6. CPU interrupt".

H) Interrupt enable flag

Enables an interrupt generation to the CPU. For details, see "6. CPU interrupt".

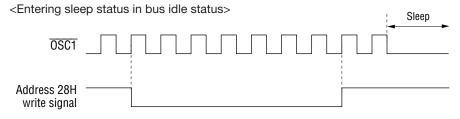

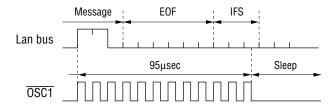

I) Sleep command register

MSM6636 enters sleep status by writing "AAH" to address 28H. In sleep status, the oscillation circuit stops and MSM6636 enters low current consumption mode. For details, see "8. Sleep function".

J) Break command register

The break command is transmitted by writing "55H" to address 29H. For details, see "10. Break function".

K) Mode setting register

This register sets the transmission speed, re-transmission function and a LAN bus output prohibit. Set this register first before initialization. For details, see MSM6636 Users Manual "3.11 Mode setting register".

L) Physical address register

Set the physical address (ID) of each node.

M) Functional address register

The functional address is the address of nodes with the same function. A maximum of 15 types of functional addresses can be set. In the case of communication by functional addressing, 15 types of address values are automatically filtered in sequence. Even if 15 types are not used for functional addressing, all functional address registers are filtered. Set the functional address value to all address areas during initialization.

N) NAK register

Response data, to be transmitted when the NAK return function is used, is written. For details, see MSM6636 Users Manual "3.14 NAK register".

## **INITIALIZING MSM6636**

### 3. INITIALIZING MSM6636

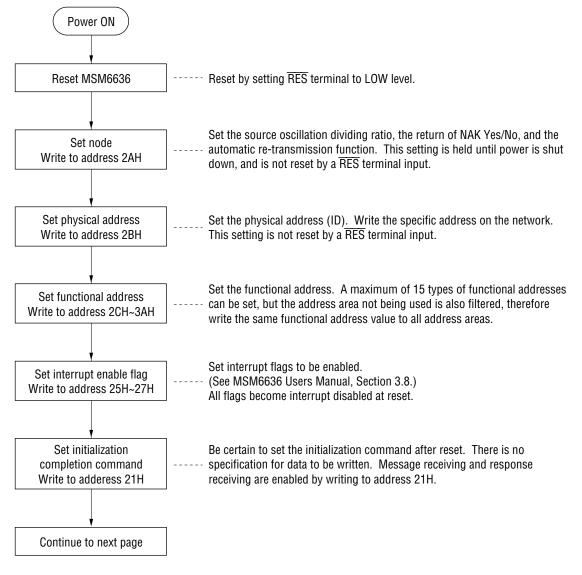

### 3.1 Initializing Node

The following is an example of initializing one node connected to the LAN.

Figure 3-1 Node Initialization Flow (2/2)

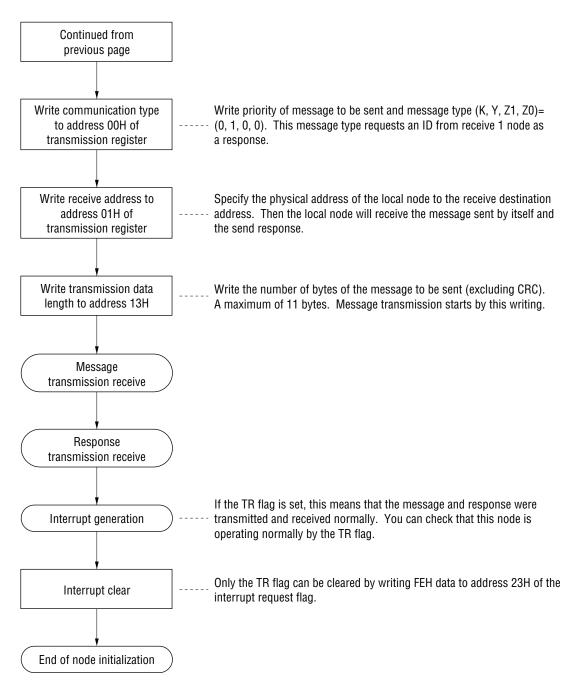

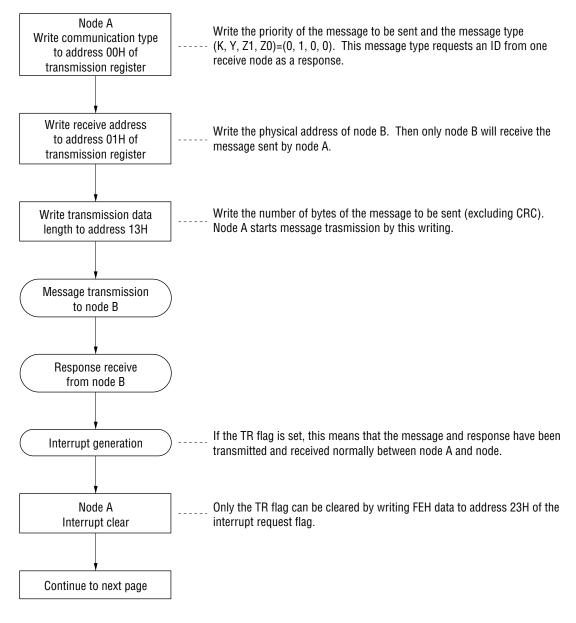

### 3.2 Initializing Network

The following is an example of checking communication status among nodes connected on the network after all nodes are initialized.

In this example, one node (node A) sends a message to all other nodes, and checks that responses are returned from each node. This operation can check that connection of all nodes on the network is normal.

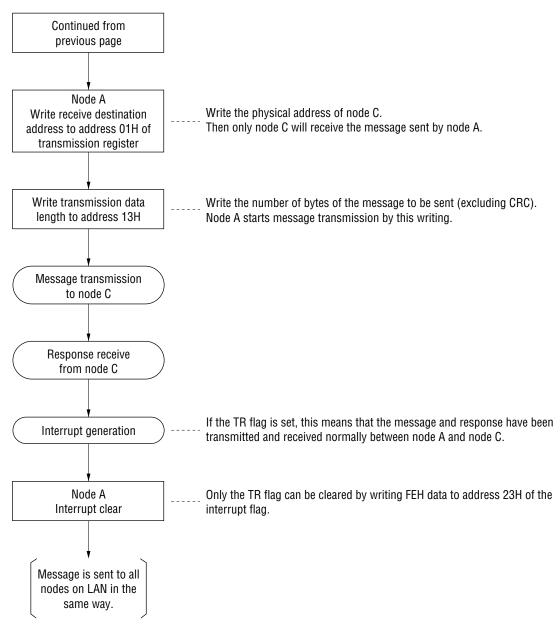

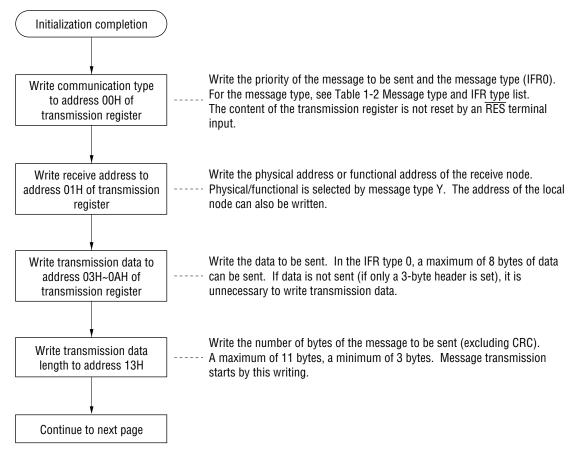

Figure 3-2 Network Initialization Flow (1/2)

Figure 3-2 Network Initialization Flow (2/2)

### **Chapter 4**

# MESAGE TRANSMISSION AND RESPONSE RECEIVE OPERATION

### 4. MESSAGE TRANSMISSION AND RESPONSE RECEIVE OPERATION

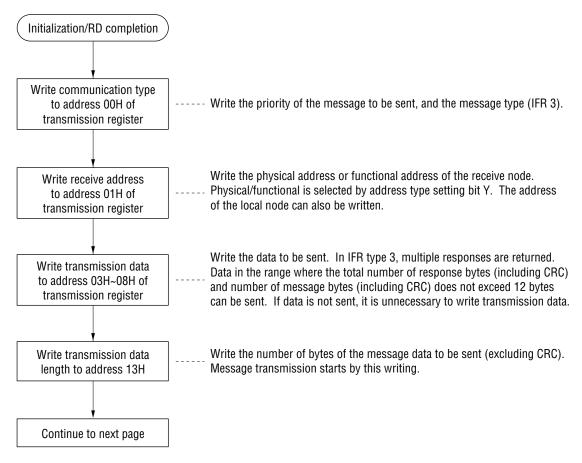

### 4.1 Message Transmission Operation of IFR Type 0

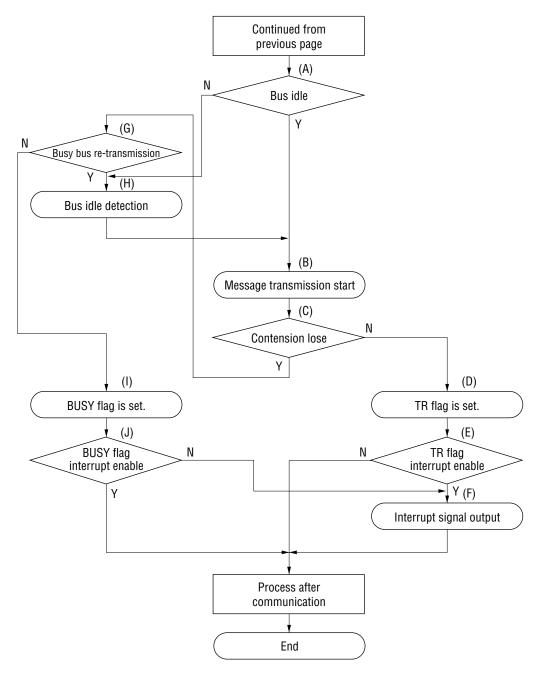

Figure 4-1 IFR Type 0 Transmission Flow (1/2)

### **OKI: Keyed Text for Preceding Page**

- (A) If the LAN bus is in idle status when writing transmission data length ends, the operation moves to B. If another node is using the LAN bus at this time, operation move to H.

- (B) Message transmission starts and operation moves to C.

- (C) If lost in contension with the message of another node, operation moves to G, otherwise operation moves to D.

- (D) If message transmission ends and "EOD" is detected, the interrupt request flag TR is set and operation moves to E.

- (E) If the interrupt enable flag for the TR flag has been set, operation moves to F. If not, the message transmission operation ends.

- (F) An interrupt signal is output from the INT terminal, and message transmission operation ends.

- (G) If the number of times of bus busy re-transmission has been set to 2 at mode setting (address 2AH), and a bus busy has not yet been resent twice, operation moves to H. If a busy bus has been sent twice, of if the setting is no re-transmission, operation moves to I.

- (H) After detecting that other nodes have finished using the LAN bus, operation moves to B.

- (I) Interrupt request flag BUSY is set, and operation moves to J.

- (J) If interrupt enable flag for the BUSY flag has been set, operation moves to F. If not, message transmission operation ends.

Figure 4-1 IFR Type 0 Transmission Flow (2/2)

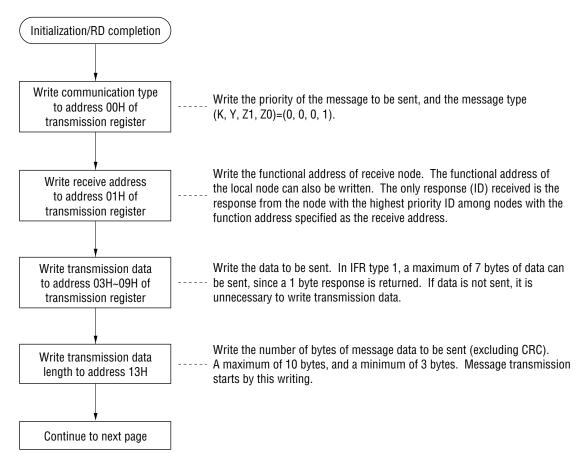

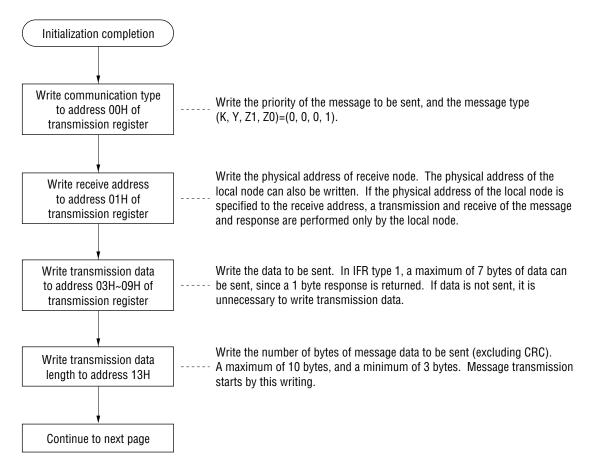

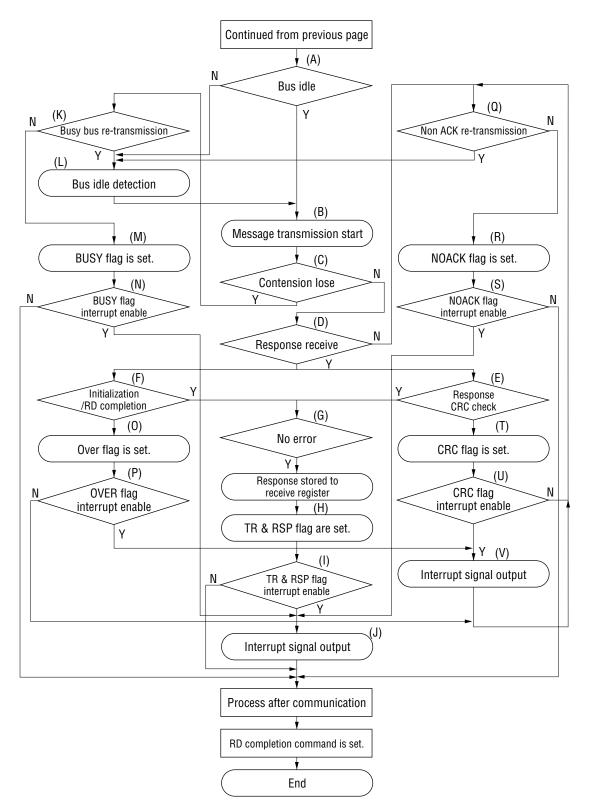

4.2 Message Transmission and Message Receive Operation of IFR Type 1 (addressing by functional address)

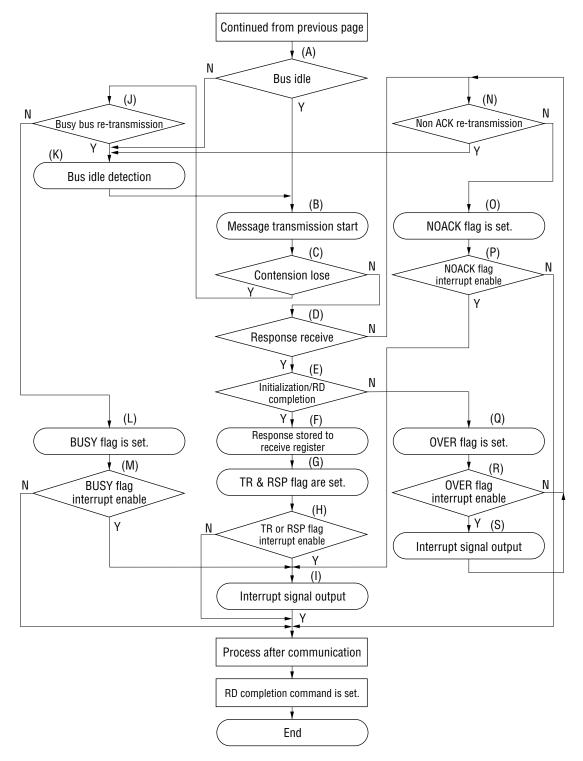

Figure 4-2 IFR Type 1 (1) Transmission Flow (1/2)

### OKI: Keyed Text for Preceding Page

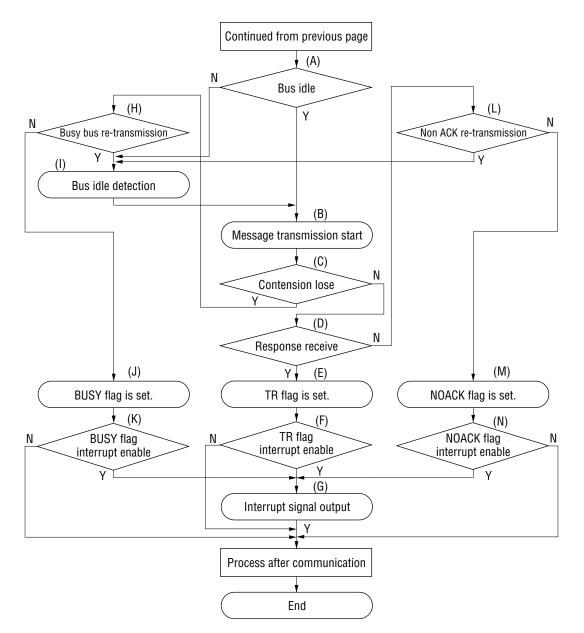

- (A) If the LAN bus is in idle status when writing transmission data length ends, operation moves to B. If another node is using the LAN bus at this time, operation moves to K.

- (B) Message transmission starts and operation moves to C.

- (C) If lost in contension with the message of another node, operation moves to J, otherwise operation moves to D.

- (D) If a response from the receive node is received normally, operation moves to E. If a response is not received, operation moves to N. Response at this time comes only from the node with the highest priority ID among nodes which received the message.

- (E) If the initialization/RD completion command (address 21H) has been set, operation moves to F. If not, operation moves to Q.

- (F) The received response is stored to the receive register (address 15H). Receive data length 01H is stored to the receive data length register (address 20H), and operation moves to G.

- (G) Interrupt request flag TR and RSP are set, and operation moves to H.

- (H) If the interrupt flag for TR or the RSP flag has been set, operation moves to I. It not, message transmission operation ends.

- (I) An interrupt signal is output from the INT terminal, and message transmission operation ends.

- (J) If the number of times of bus busy re-transmission has been set to 2 at mode setting (address 2AH), and a busy bus has not yet been resent twice, operation moves to K. If a busy bus has been sent twice, or if the setting is no re-transmission, operation moves to L.

- (K) After detecting that other nodes finished using the LAN bus, operation moves to B.

- (L) The interrupt request flag BUSY is set, and operation moves to M.

- (M) If an interrupt enable flag for the BUSY flag has been set, operation moves to I. If not, message transmission operation ends.

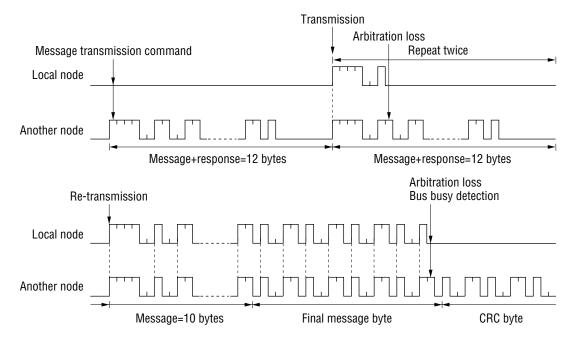

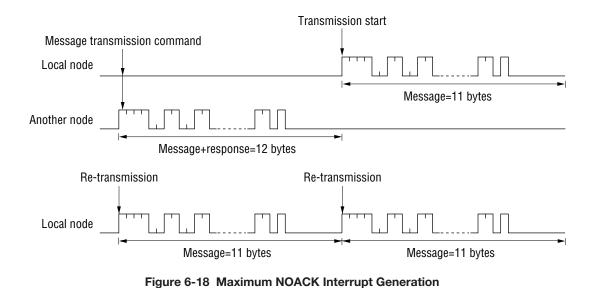

- (N) If the number of times to of a non ACK re-transmission has been set to 2 at mode setting (address 2AH), and a non ACK has not yet been resent twice, operation moves to K. If a non ACK has been sent twice, or if the setting is no re-transmission, operation moves to O.

- (O) The interrupt request flag NOACK is set, and operation moves to P.

- (P) If the interrupt enable flag for NOACK has been set, operation moves to I. If not, message transmission operation ends.

- (Q) The interrupt request flag OVER is set, and operation moves to R. The response received at this time is not stored to the receive register.

- (R) If the interrupt enable flag for the OVER flag has been set, operation moves to S. If not, operation moves to N.

- (S) An interrupt signal is output from the INT terminal, and operation moves to N.

Figure 4-2 IFR Type 1 (1) Transmission Flow (2/2)

4-7 SUNSTAR电子元器件 http://www.sunstare.com/ TEL: 0755-83778810 FAX:0755-83376182 E-MAIL:szss20@163.com 4.3 Message Transmission and Response Receive Operation of IFR Type 1 (addressing by physical address)

Figure 4-3 IFR Type 1 (2) Transmission Flow (1/2)

# **OKI: Keyed Text for Preceding Page**

- (A) If the LAN bus is in idle status when writing transmission data length ends, operation modes to B. If another node is using the LAN bus at this time, operation moves to I.

- (B) Message transmission starts and operation moves to C.

- (C) If lost in contension with the message of another node, operation moves to H, otherwise operation moves to D.

- (D) If the received response and address value specified as the receive address match, operation moves to E. If there is no match, or if a response was not returned, operation moves to L.

- (E) Interrupt request flag TR is set, and operation moves to F. The response received at this time is not stored to the receive register, nor is the receive data length stored either.

- (F) If the interrupt enable flag for the TR flag has been set, operation moves to G. If not, message transmission operation ends.

- (G) An interrupt signal is output from the INT terminal, and message transmission operation ends.

- (H) If the number of times of bus busy re-transmission has been set to 2 at mode setting (address 2AH), and a busy bus has not yet been resent twice, operation moves to I. If a busy bus has been sent twice, or if the setting is no re-transmission, operation moves to J.

- (I) After detecting that other nodes finished using the LAN bus, operation moves to B.

- (J) The interrupt request flag BUSY is set, and operation moves to K.

- (K) If an interrupt enable flag for the BUSY flag has been set, operation moves to G. If not, message transmission operation ends.

- (L) If the number of times of non ACK re-transmission has been set to 2 at mode setting (address 2AH), and a non ACK has not yet been resent twice, operation moves to I. If a non ACK has been sent twice, or if the setting is no re-transmission, operation moves to M.

- (M) The interrupt request flag NOACK is set, and operation moves to N.

- (N) If the interrupt enable flag for NOACK has been set, operation moves to G. If not, message transmission operation ends.

Figure 4-3 IFR Type 1 (2) Transmission Flow (2/2)

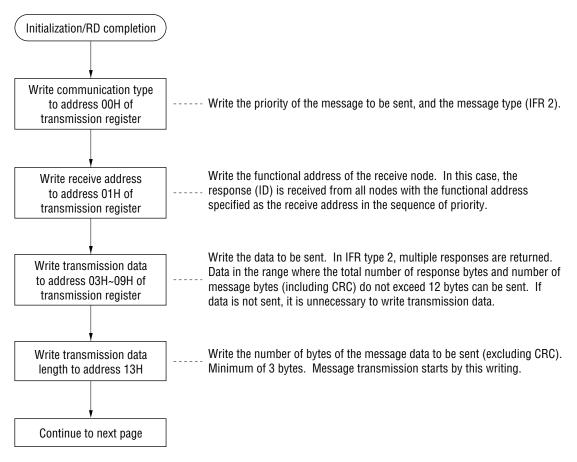

4.4 Message Transmission and Response Receive Operation of IFR Type 2

Figure 4-4 IFR Type 2 Transmission Flow (1/2)

A~S except D and F, are the same as 4.2 IFR type 1 (addressing by functional address)

- (D) If responses from all receive nodes are received, operation moves to E, and if responses are not returned, operation moves to N. A maximum of 8 bytes of response can be received when the transmission data length (13H) is 3 bytes (excluding CRC).

- (F) All received responses are stored from address 15H of the receive register in the sequence of priority. The receive data length (number of bytes of received responses) is stored to the receive data length register (address 20H), and operation moves to G.

Figure 4-4 IFR Type 2 Transmission Flow (2/2)

4-12 SUNSTAR电子元器件 http://www.sunstare.com/ TEL: 0755-83778810 FAX:0755-83376182 E-MAIL:szss200163.com

# 4.5 Message Transmission and Response Receive Operation of IFR Type 3

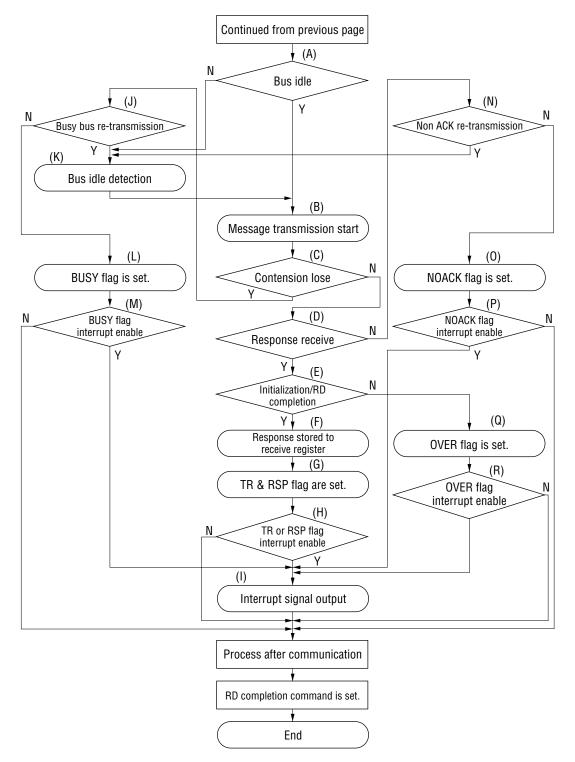

Figure 4-5 IFR Type 3 Transmission Flow (1/2)

# **OKI: Keyed Text for Preceding Page**

- (A) If the LAN bus is in idle status when writing transmission data length ends, operation modes to B. If another node is using the LAN bus at this time, operation moves to L.

- (B) Message transmission starts and operation moves to C.

- (C) If lost in contension with the message of another node, operation moves to K, otherwise operation moves to D.

- (D) If responses from all the receive nodes are received, operation moves to E and F, and if responses are not received, operation moves to Q.

- (E) The CRC code of the received response is checked. If normal, operation moves to G, and if an error is detected, operation moves to T.

- (F) If the initialization/RD completion command (address 21H) has been set, operation moves to G. If not, operation moves to O.

- (G) If a CRC error and OVER error are not detected, all received responses are stored from address 15H of the receive register. The receive data length (excluding CRC) is stored to the receive data length register (address 20H), and operation moves to H.

- (H) Interrupt request flag TR and RSP are set, and operation moves to I.

- (I) If the interrupt enable flag for TR or the RSP have been set, operation moves to J. If not, message transmission operation ends.

- (J) An interrupt signal is output from the INT terminal, and message transmission operation ends.

- (K) If the number of times of bus busy re-transmission has been set to 2 at mode setting (address 2AH), and a busy bus has not yet been resent twice, operation moves to L. If a busy bus has been sent twice, or if the setting is no re-transmission, operation moves to M.

- (L) After detecting that other nodes finished using the LAN bus, operation moves to B.

- (M) The interrupt request flag BUSY is set, and operation moves to N.

- (N) If an interrupt enable flag for the BUSY flag has been set, operation moves to J. If not, message transmission operation ends.

- (O) Interrupt request flag OVER is set, and operation moves to P.

- (P) If the interrupt enable flag for the OVER flag has been set, operation moves to V. If not, operation moves to Q.

- (Q) If the number of times of non ACK re-transmission has been set to 2 at mode setting (address 2AH), and a non ACK has not yet been resent twice, operation moves to L. If a non ACK has been sent twice, or if the setting is no re-transmission, operation moves to R.

- (R) The interrupt request flag NOACK is set, and operation moves to S.

- (S) If the interrupt enable flag for NOACK has been set, operation moves to J. If not, message transmission operation ends.

- (T) Interrupt request flag CRC is set, and operation moves to U.

- (U) If the interrupt enable flag for the CRC flag has been set, operation moves to V, if not, operation moves to Q.

- (V) An interrupt signal is output from the INT terminal, and operation moves to Q.

Figure 4-5 IFR Type 3 Transmission Flow (2/2)

4-16 SUNSTAR电子元器件 http://www.sunstare.com/ TEL: 0755-83778810 FAX:0755-83376182 E-MAIL:szss20@163.com

# Chapter 5

# MESSAGE RECEIVE AND RESPONSE TRANSMISSION OPERATION

# 5. MESSAGE RECEIVE AND RESPONSE TARNSMISSION OPERATION

# 5.1 Message Receive Operation of IFTR Type 0

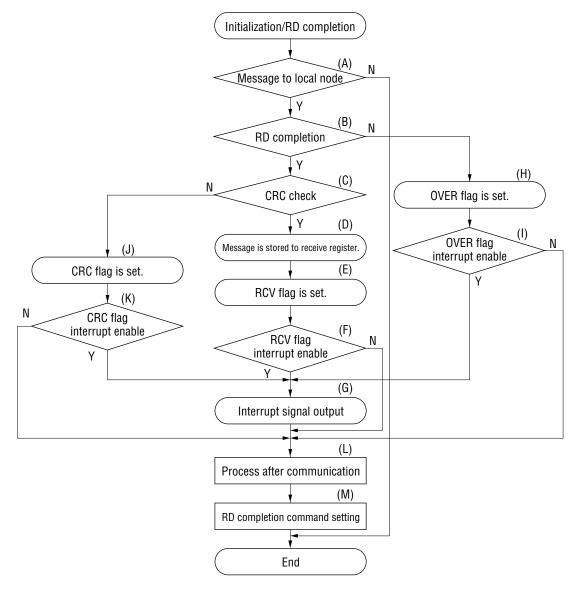

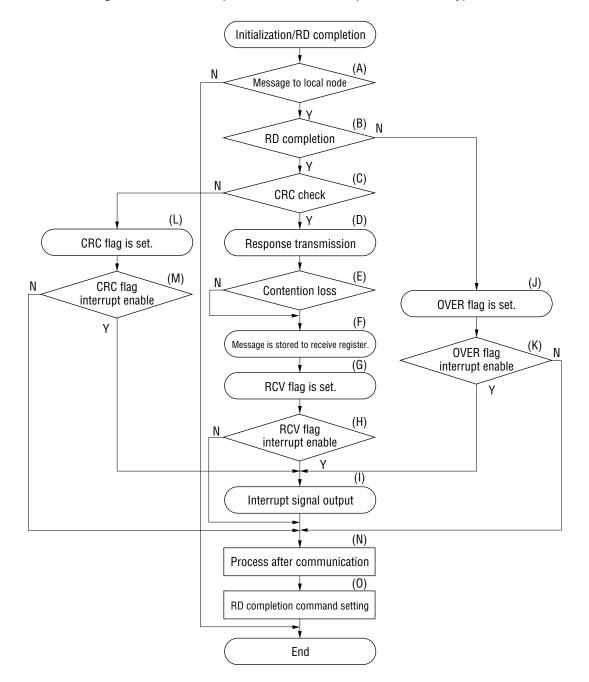

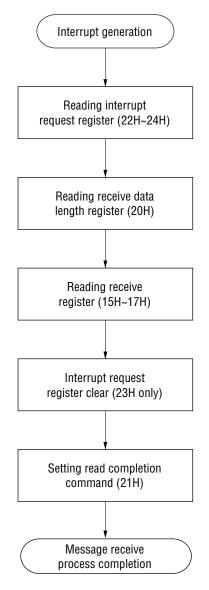

Figure 5-1 IFR Type 0 Receive Flow

- (A) Receive address of received message and physical or functional address of local node are compared. Only if matched, the message is judged as a message to the local node, and operation moves to B. If not matched, receive operation ends.

- (B) If the RD completion command has been set before receiving "EOD", operation moves to C. If not, operation moves to H.

- (C) The CRC code of the received message is checked. If normal, operation moves to D, if an error is detected, operation moves to J.

- (D) All received messages are stored from address 15H of the receive register, and operation moves to E. The receive data length (excluding CRC) is stored to the receive data length register (address 20H).

- (E) The interrupt request flag RCV is set, and operation moves to F.

- (F) If the interrupt of the RCV flag is enabled, operation moves to G, and if not, the message receive operation ends, and operation moves to L.

- (G) An interrupt signal is output from the INT terminal, the message receive operation ends, and operation moves to L.

- (H) The interrupt request flag OVER is set, and operation moves to I.

- (I) If the interrupt of the OVER flag is enabled, operation moves to G, and if not, the message receive operation ends, and operation moves to L.

- (J) The interrupt request flag CRC is set, and operation moves to K.

- (K) If the interrupt of the CRC flag is enabled, operation moves to G, and if not, the message receive operation ends, and operation moves to L.

- (L) Processes after communication (reading receive register, clearing interrupt request flag, etc.) is performed.

- (M) The RD completion command (address 21H) is set. This setting enables receiving the next message and response.

### 5.2 Message Receive and Response Transmission Operation of IFR Type 1

Figure 5-2 IFR Type 1 Receive Flow

- (A) Receive address of received message and physical or functional address of local node are compared. Only if matched, the message is judged as a message to the local node, and operation moves to B. If not matched, receive operation ends.

- (B) If the RD completion command has been set before receiving "EOD", operation moves to C. If not, operation moves to J.

- (C) The CRC code of the received message is checked. If normal, operation moves to D, if an error is detected, operation moves to L.

- (D) The physical address value of the local node is sent as the response, and operation moves to E.

- (E) If lost in contention with the response of another node, response transmission stops, and operation moves to F. Even if loss is not detected, operation still moves to F.

- (F) All received messages are stored from address 15H of the receive register, and operation moves to G. The response is not stored. The number of bytes of the received message (excluding CRC and response) is stored to the receive message length register (address 20H).

- (G) The interrupt request flag RCV is set, and operation moves to H.

- (H) If the interrupt of the RCV flag is enabled, operation moves to I, and if not, the message receive operation ends, and operation moves to N.

- (I) An interrupt signal is output from the INT terminal, message receive operation ends, and operation moves to N.

- (J) The interrupt request flag OVER is set, and operation moves to K.

- (K) If the interrupt of the OVER flag is enabled, operation moves to I, and if not, message receive operation ends, and operation moves to N.

- (L) The interrupt request flag CRC is set, and operation moves to K.

- (M) If the interrupt of the CRC flag is enabled, operation moves to I, and if not, message receive operation ends, and operation moves to N.

- (N) Processes after communication (reading receive register, clearing interrupt request flag, etc.) is performed.

- (O) The RD completion command (address 21H) is set. This setting enables receiving the next message and response.

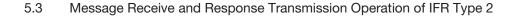

Figure 5-3 IFR Type 2 Receive Flow

- (A) The receive address of the received message and the functional address of the local node are compared. Only if matched, the message is judged as the message to the local node, and operation moves to B. If not matched, receive operation ends.

- (B) If the RD completion command has been set before receiving "EOD", operation moves to C. If not, operation moves to K.

- (C) The CRC code of the received message is checked. If normal, operation moves to D, if an error is detected, operation moves to M.

- (D) The physical address value of the local node is sent as the response, and operation moves to E.

- (E) If lost in with the response of another node, operation moves to J. If not, operation moves to F.

- (F) All received messages are stored from address 15H of the receive register, and operation moves to G. The response is not stored. The number of bytes of the received message (excluding CRC and response) is stored to the receive message length register address (20H).

- (G) The interrupt request flag RCV is set, and operation moves to H.

- (H) If the interrupt of the RCV flag is enabled, operation moves to I, and if not, the message receive operation ends, and operation moves to O.

- (I) An interrupt signal is output from the INT terminal, message receive operation ends, and operation moves to O.

- (J) If the end of an 8-bit transmission of the response from another node is detected, operation moves to D. If not (response transmission stopped due to noise, etc.), message receive operation ends.

- (K) The interrupt request flag OVER is set, and operation moves to L.

- (L) If the interrupt of the OVER flag is enabled, operation moves to I, and if not, message receive operation ends, and operation moves to O.

- (M) The interrupt request flag CRC is set, and operation moves to N.

- (N) If the interrupt of the CRC flag is enabled, operation moves to I, and if not, message receive operation ends, and operation moves to O.

- (O) Processes after communication (reading receive register, clearing interrupt request flag, etc.) is performed.

- (P) The RD completion command (address 21H) is set. This setting enables receiving the next message and response.

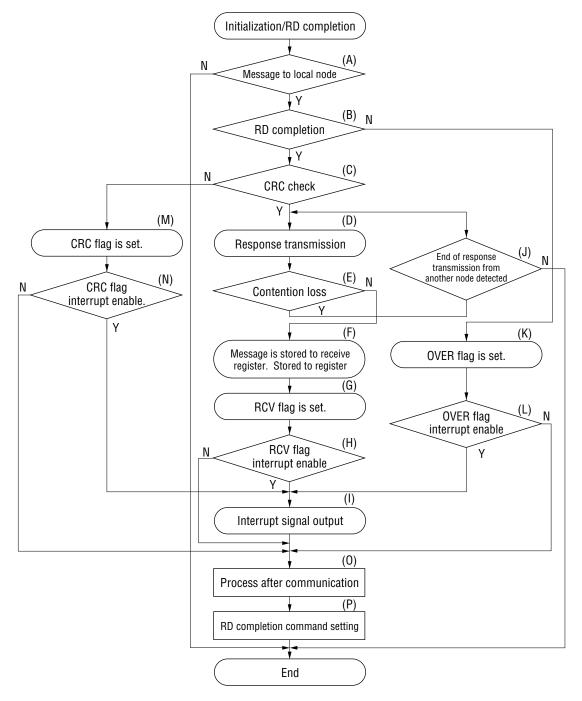

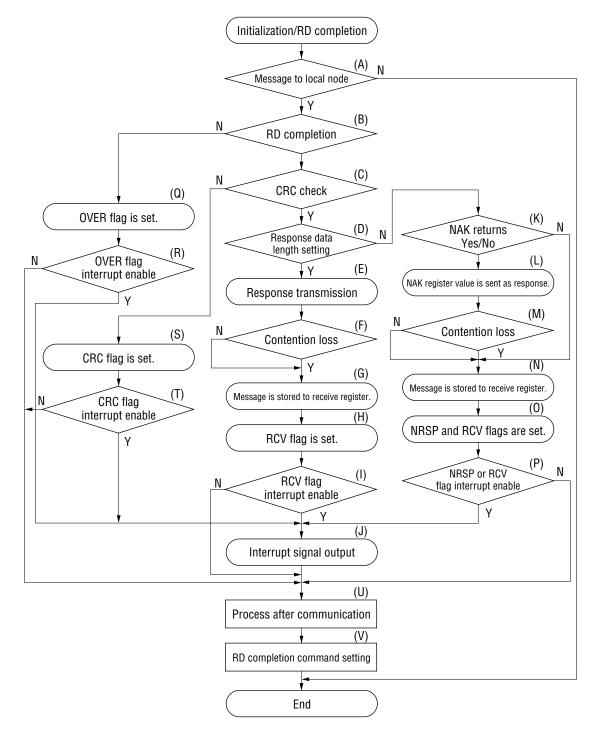

# 5.4 Message Receive and Response Transmission Operation of IFR Type 3

Figure 5-4 IFR Type 3 Receive Flow

**5-7** SUNSTAR电子元器件 http://www.sunstare.com/ TEL: 0755-83778810 FAX:0755-83376182 E-MAIL:szss20@163.com

- (A) Receive address of received message and physical or functional address of local node are compared. Only if matched, the message is judged as a message to the local node, and operation moves to B. If not matched, receive operation ends.

- (B) If the RD completion command has been set before receiving "EOD", operation moves to C. If not, operation moves to Q.

- (C) The CRC code of the received message is checked. If normal, operation moves to D, if an error is detected, operation moves to S.

- (D) If the response data length address (14H) has been set before receiving "EOD", operation moves to E. If not, operation moves to K.

- (E) The data stored from address 0BH of the response register is sent for the number of bytes specified by the response data length (address 14H) as the response, and operation moves to F. CRC code is automatically added at the end of the response.

- (F) If lost in contention with the response of another node, response transmission stops, and operation moves to G. Even if loss is not detected, operation still moves to G.

- (G) All received messages are stored from address 15H of the receive register, and operation moves to H. The response is not stored. The number of bytes of the received message (excluding CRC and response) is stored to the receive message length register (address 20H).

- (H) The interrupt request flag RCV is set, and operation moves to I.

- (I) If the interrupt of the RCV flag is enabled, operation moves to J, and if not, the message receive operation ends, and operation moves to U.

- (J) An interrupt signal is output from the INT terminal, message receive operation ends, and operation moves to U.

- (K) If NAK return has been set to returning the NAK register value at the mode setting (address 2AH), operation moves to L. If set to no IFR, operation moves to N.

- (L) The value of the NAK register (address 3BH) is sent as the response, and operation moves to M. CRC code is automatically added at the end of the response.

- (M) If lost in contention with the response of another node, response transmission stops, and operation moves to N. Even if loss is not detected, operation still moves to N.

- (N) All received messages are stored from address 15H of the receive register, and operation moves to O. The response is not stored. The number of bytes of the received message (excluding CRC and response) is stored to the receive message length register address 20H).

- (O) Interrupt request flags NRSP and RCV are set, and operation moves to P.

- (P) If the interrupt of NRSP or RCP flags is enabled, operation moves to J, and if not, message receive operation ends, and operation moves to U.

- (Q) The interrupt request flag OVER is set, and operation moves to R.

- (R) If the interrupt of the OVER flag is enabled, operation moves to J, and if not, message receive operation ends, and operation moves to U.

- (S) The interrupt request flag CRC is set, and operation moves to T.

- (T) If the interrupt of the CRC flag is enabled, operation moves to J, and if not, message receive operation ends, and operation moves to U.

- (U) Processes after communication (reading receive register, clearing interrupt request flag, etc.) is performed.

- (V) The RD completion command (address 21H) is set. This setting enables receiving the next message and response.

# **CPU INTERRUPT**

SUNSTAR电子元器件 http://www.sunstare.com/ TEL: 0755-83778810 FAX:0755-83376182 E-MAIL:szss200163.com

# 6. CPU INTERRUPT

When transmission/receive is completed, or when various errors occur, an interrupt can be requested to the host CPU by an INT output (low active). Also an interrupt enable/disable can be set for each interrupt factor.

<Interrupt request flag>

|     | MSB |     |     |      |     |      |     | LSB | _ |

|-----|-----|-----|-----|------|-----|------|-----|-----|---|

| 22H | LEN | ABN | D-P | OVER | CRC | FORM | INV | IFS |   |

Message abnormality, etc.

|     | MSB  |       |      |   |     |     |     | LSB |  |

|-----|------|-------|------|---|-----|-----|-----|-----|--|

| 23H | BUSY | NOACK | NRSP | _ | BRK | RSP | RCV | TR  |  |

Message transmission/receive status, etc.

|     | MSB |   |      |      |     |     |     | LSB |

|-----|-----|---|------|------|-----|-----|-----|-----|

| 24H | PAR | _ | WAKR | WAKD | BPG | BPV | BNG | BNV |

LAN bus line related, etc.

"1" indicates that a corresponding interrupted was generated. If a bit to which a flag is not assigned is read, "0" is read. All bits are automatically set to "0" at reset.

<Interrupt enable flag>

|     | MSB |     |     |      |     |      |     | LSB |

|-----|-----|-----|-----|------|-----|------|-----|-----|

| 25H | LEN | ABN | D-P | OVER | CRC | FORM | INV | IFS |

Message abnormality, etc.

|     | MSB  |       |      |   |     |     |     | LSB |

|-----|------|-------|------|---|-----|-----|-----|-----|

| 26H | BUSY | NOACK | NRSP | _ | BRK | RSP | RCV | TR  |

Message transmission/receive status, etc.

|     | MSB |   |      |      |     |     |     | LSB |

|-----|-----|---|------|------|-----|-----|-----|-----|

| 27H | PAR | _ | WAKR | WAKD | BPG | BPV | BNG | BNV |

LAN bus line related, etc.

"1" enables a corresponding interrupt. All bits are automatically set to "0" at reset. A bit to which a flag is not assigned can also be written, and the written value can be read. Even if "1" is written to a bit to which a flag is not assigned, this bit does not generate an interrupt.

An interrupt is cleared by writing "0" to the corresponding bit of the interrupt request flag by which an interrupt is generated. Even if "1" is written to the interrupt request flag, the flag is not set and the previous status is held. Therefore by writing "0" only to the bits corresponding to the factor to be cleared, and by writing "1" to the other bits, another interrupt can be accepted during a clear operation.

An interrupt request is cleared when all bit set to interrupt enable status are cleared.

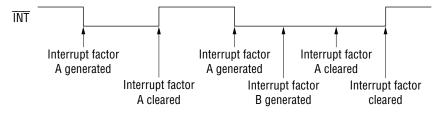

Figure 6-1 Clearing Interrupt Request

# 6.1 Receive Message Length Error Interrupt (LEN)

This interrupt is generated when the frame length of a receive message exceeds 12 bytes (including CRC). Only the message transmission node and message receive node generate this interrupt. The node which transmits the message must determine the transmission data length (excluding CRC) considering the number of bytes of a response, so that the frame length of the message does not exceed 12 bytes.

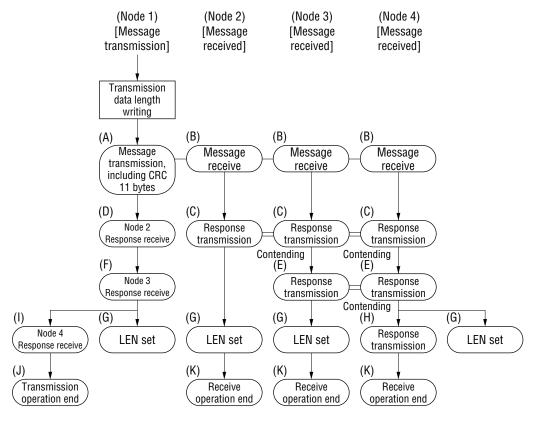

For example, when 10 bytes of an IFR type 2 message (excluding CRC) is sent, and the response is 3 bytes (3 nodes receive this message), the operation of the message transmission node and the 3 message receive nodes become as follows.

Figure 6-2 Example of LEN Interrupt Flow (in the case of message 10 bytes and response 3 bytes)

- (A) Node 1 sends an IFR type 2 message to Nodes 2, 3 and 4. This transmission data length is 11 bytes, including CRC.

- (B) Nodes 2, 3 and 4 receive the message sent from Node 1.

- (C) When the message from Node 1 is received, Nodes 2, 3 and 4 start sending a response at the same time. If the priority of the response (physical address value) at this time is node >Node 3>Node 4, Nodes 3 and 4 detect loss, and they stop sending a response.

- (D) Node 1 receives a response from Node 2.

- (E) When the response transmission of Node 2 ends, Nodes 3 and 4 start a response transmission again. Node 4 detects loss again, and it stops sending a response.

- (F) Node 1 receives a response from Node 3.

- (G) When the response transmission of Node 3 ends, the frame length of the message becomes 13 bytes. Nodes 1, 2, 3 and 4 set the receive message length error flag LEN.

- (H) When the response transmission of Node 3 ends, Node 4 starts a response transmission again. Although a receive message length error flag LEN has been detected at this time, response transmission is continued.

- (I) Node 1 receives a response from Node 4.

- (J) When Node 1 receives a response from Node 4, message transmission operation ends. Response node 1 received is not stored to the response register. At this time the interrupt request flag LEN and NOACK have been set (when the number of times of re-transmission at non ACK is set to "no re-transmission").

- (K) When the response transmission of Node 4 ends, Nodes 2, 3 and 4 end message receive operation. The message sent from Node 1 is not stored to the receive register. At this time the interrupt request flag LEN has been set.

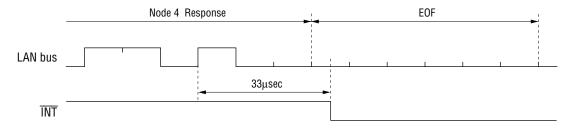

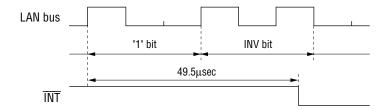

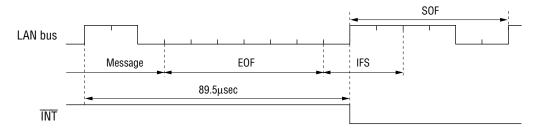

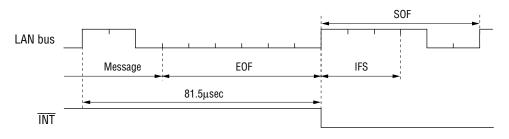

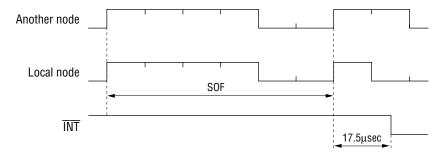

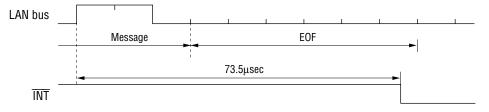

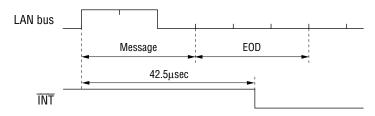

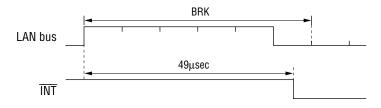

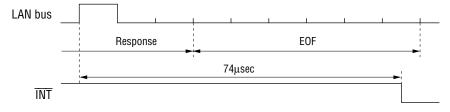

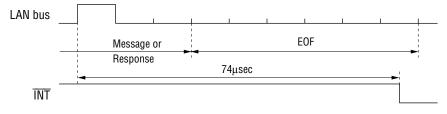

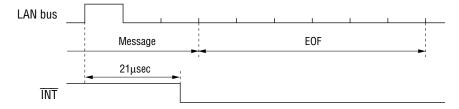

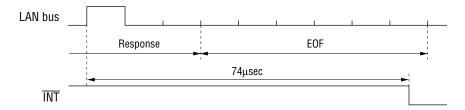

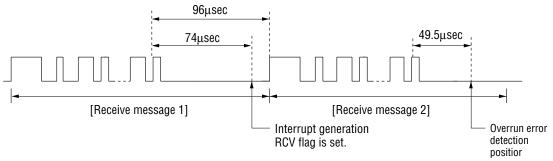

Interrupt generation timing is shown below (when the transmission speed setting is 41.6 Kbps).

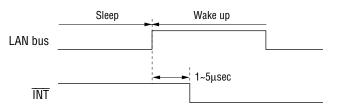

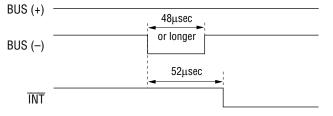

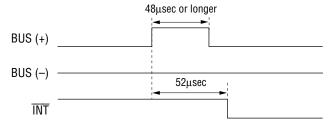

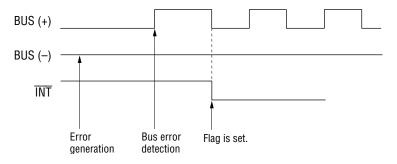

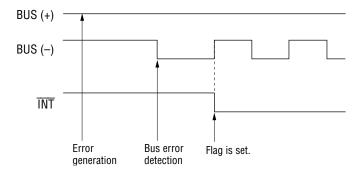

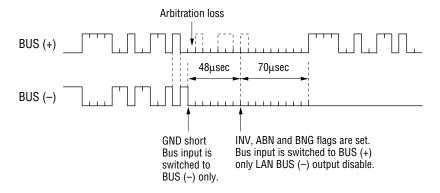

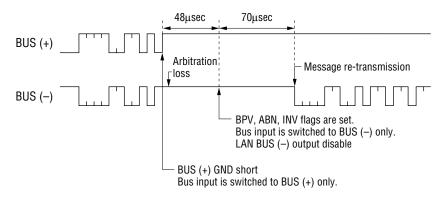

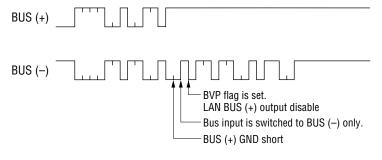

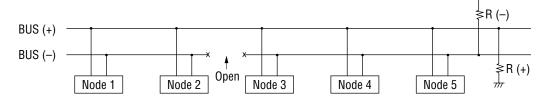

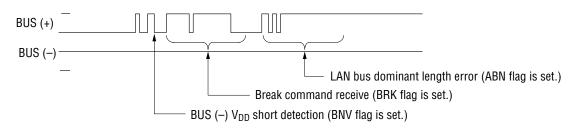

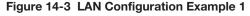

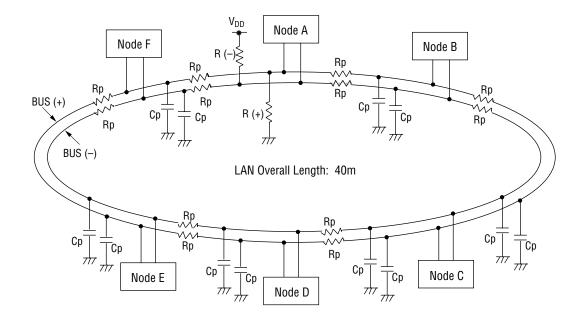

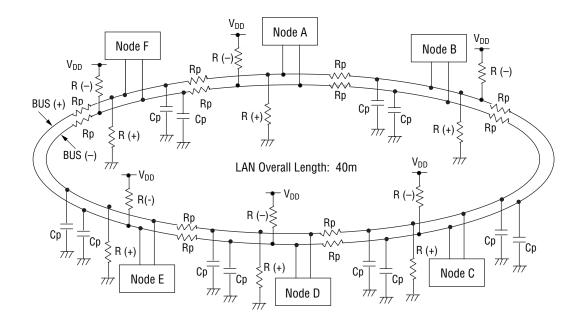

Figure 6-3 LEN Interrupt Generation Timing